# 带 OCDS 功能 LCD 型血糖仪 Flash 单片机

# BH67F2472

版本: V1.21 日期: 2021-11-01

www.holtek.com

## 目录

| 特性                     | 7  |

|------------------------|----|

| CPU 特性                 | 7  |

| 周边特性                   | 7  |

| 开发工具                   | 8  |

| 概述                     | 8  |

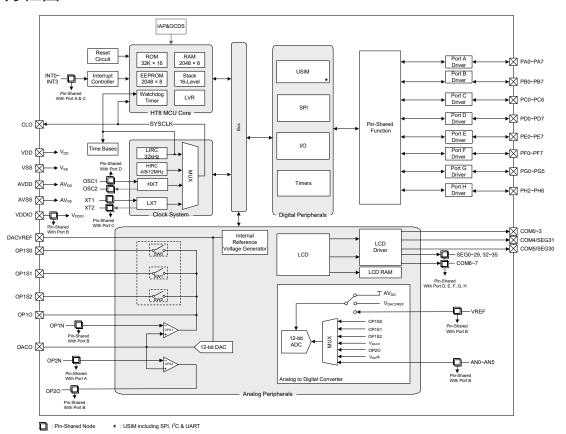

| 方框图                    | 9  |

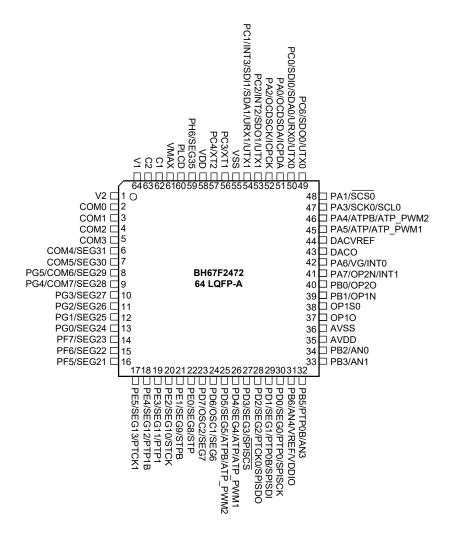

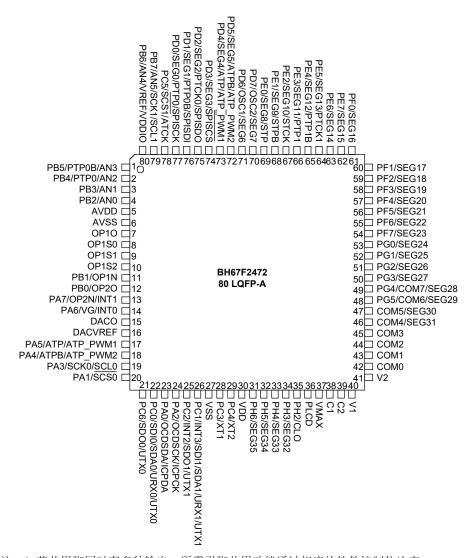

| 引脚图                    | 10 |

| 引脚说明                   |    |

| 极限参数                   |    |

| 直流电气特性                 |    |

| 工作电压特性                 |    |

| 工作电流特性                 |    |

|                        |    |

| 交流电气特性                 | 20 |

| 内部高速 RC 振荡器 HIRC 频率精准度 |    |

| 内部低速振荡器 LIRC 电气特性      |    |

| 外部低速晶体振荡器 LXT 电气特性     | 21 |

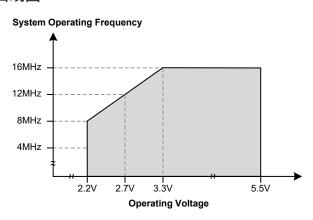

| 工作频率电气特性曲线图            | 21 |

| 系统上电时间电气特性             | 22 |

| 输入/输出口电气特性             | 22 |

| 输入/输出口(非多电源引脚)直流电气特性   |    |

| 输入/输出口(多电源引脚)直流电气特性    | 23 |

| 存储器电气特性                | 24 |

| LVR 电气特性               | 24 |

| 模拟前端电路特性               | 25 |

| 运算放大器电气特性              | 25 |

| 内部参考电压特性               |    |

| 模拟开关电气特性               |    |

| 12-bit D/A 转换器电气特性     |    |

| A/D 转换器电气特性            |    |

| LCD 驱动器电气特性            | 27 |

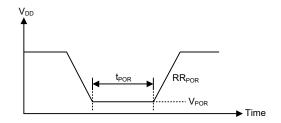

| 上电复位特性                 | 27 |

| 系统结构                   | 28 |

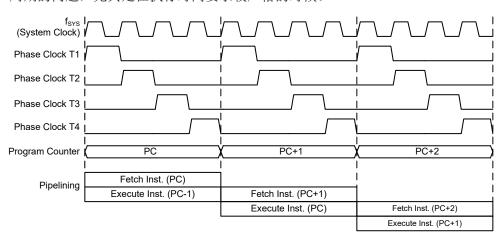

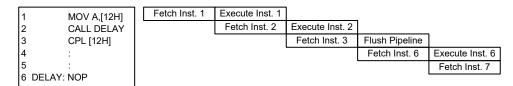

| 时序和流水线结构               | 28 |

| 程序计数器                  |    |

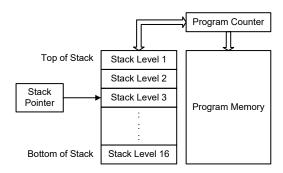

| 堆栈                     |    |

| 算术逻辑单元 – ALU           | 30 |

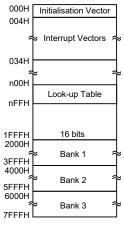

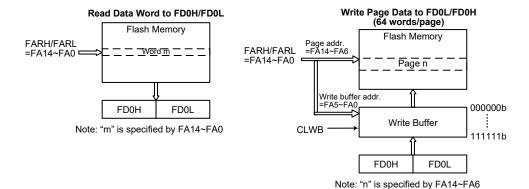

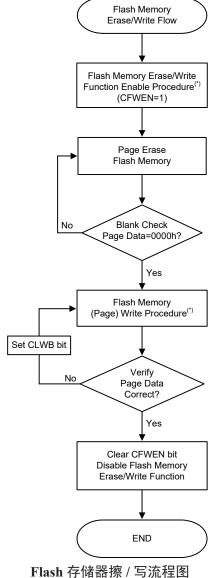

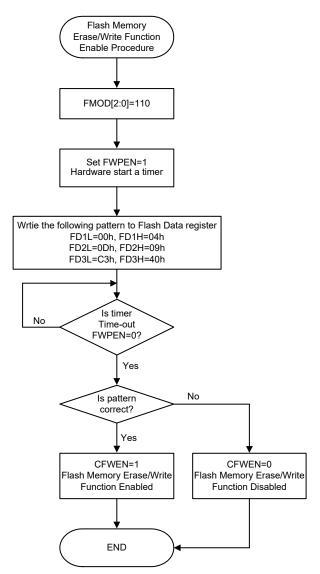

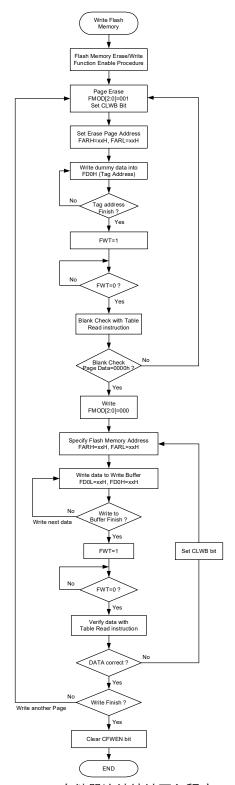

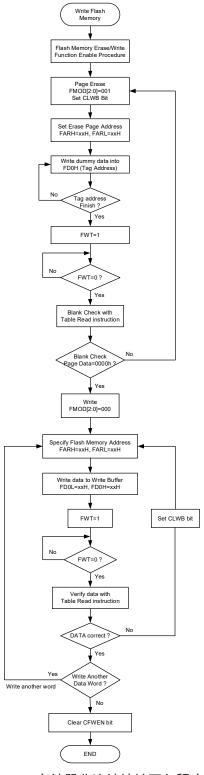

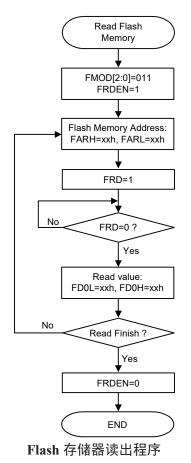

| Flash 程序存储器            |    |

| 结构                     |    |

| 特殊向量                   | 31 |

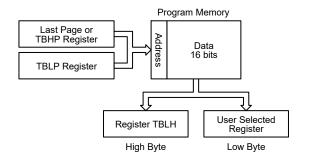

| 查表                                | 31 |

|-----------------------------------|----|

| 查表范例                              | 31 |

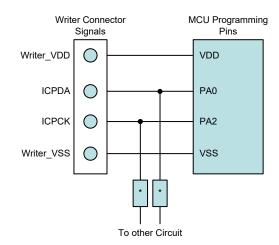

| 在线烧录 – ICP                        | 32 |

| 片上调试 – OCDS                       | 33 |

| 在线应用编程 – IAP                      | 33 |

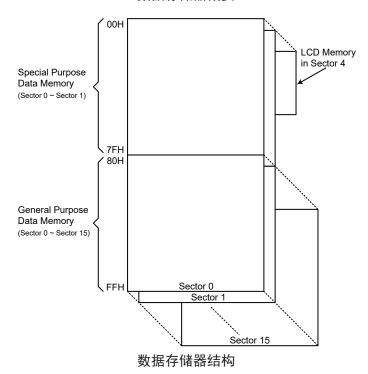

| 数据存储器                             | 47 |

| 结构                                | 47 |

| 数据存储器寻址                           | 48 |

| 通用数据存储器                           | 48 |

| 特殊功能数据存储器                         | 48 |

| 特殊功能寄存器                           | 50 |

| 间接寻址寄存器 – IAR0, IAR1, IAR2        | 50 |

| 存储器指针 – MP0, MP1H/MP1L, MP2H/MP2L | 50 |

| 程序存储区指针 – PBP                     | 51 |

| 累加器 – ACC                         | 52 |

| 程序计数器低字节寄存器 – PCL                 | 52 |

| 表格寄存器 – TBLP, TBHP, TBLH          | 52 |

| Option 存储器映射寄存器 – ORMC            | 52 |

| 状态寄存器 – STATUS                    | 53 |

| EEPROM 数据存储器                      | 54 |

| EEPROM 数据存储器结构                    | 54 |

| EEPROM 寄存器                        | 54 |

| EEPROM 读操作                        | 56 |

| EEPROM 页擦操作                       | 57 |

| EEPROM 写操作                        |    |

| 写保护                               |    |

| EEPROM 中断                         | 58 |

| 编程注意事项                            | 58 |

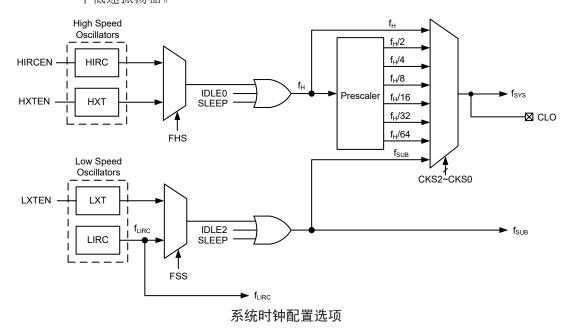

| 振荡器                               | 62 |

| 振荡器概述                             | 62 |

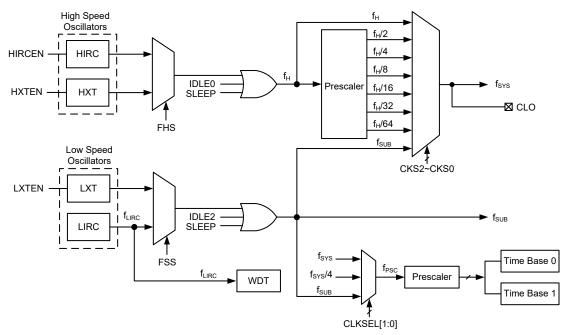

| 系统时钟配置                            | 62 |

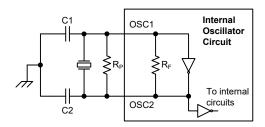

| 外部晶体 / 陶瓷振荡器 – HXT                |    |

| 内部 RC 振荡器 – HIRC                  |    |

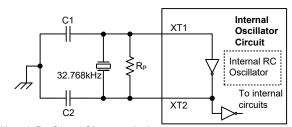

| 外部 32.768kHz 晶体振荡器 – LXT          |    |

| 内部 32kHz 振荡器 – LIRC               | 64 |

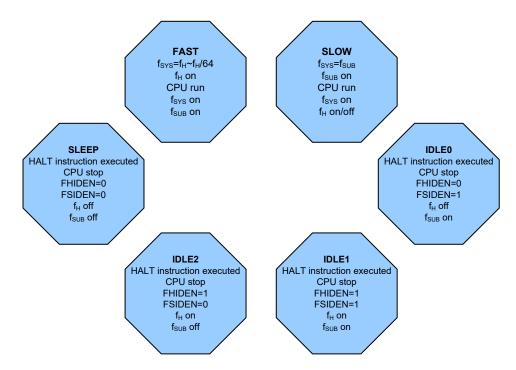

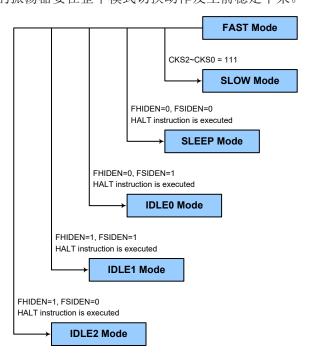

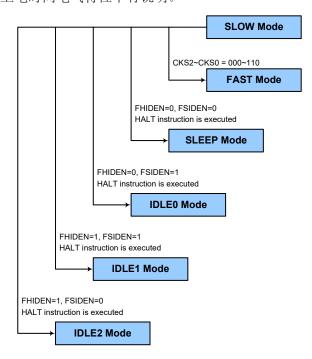

| 工作模式和系统时钟                         | 65 |

| 系统时钟                              | 65 |

| 系统工作模式                            |    |

| 控制寄存器                             |    |

| 工作模式切换                            |    |

| 待机电流的注意事项                         |    |

| 唤醒                                |    |

| 编程注意事项                            |    |

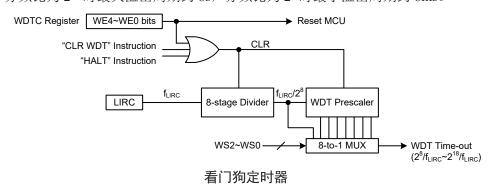

| 看门狗定时器             | 73  |

|--------------------|-----|

| 看门狗定时器时钟源          | 73  |

| 看门狗定时器控制寄存器        | 73  |

| 看门狗定时器操作           | 74  |

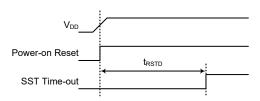

| 复位和初始化             | 75  |

| 复位功能               | 75  |

| 复位初始状态             | 78  |

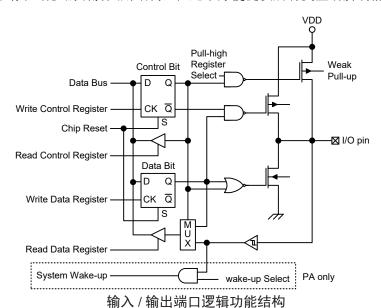

| 输入/输出端口            | 84  |

| 上拉电阻               | 85  |

| PA 口唤醒             |     |

| 输入/输出端口控制寄存器       |     |

| 输入/输出端口电源控制        |     |

| 引脚共用功能             |     |

| 输入/输出引脚结构          |     |

| 编程注意事项             | 95  |

| 定时器模块 – TM         | 96  |

| 简介                 | 96  |

| TM 操作              |     |

| TM 时钟源             |     |

| TM 中断              |     |

| TM 外部引脚            |     |

| 编程注意事项             |     |

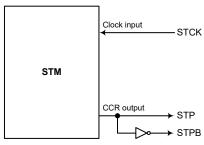

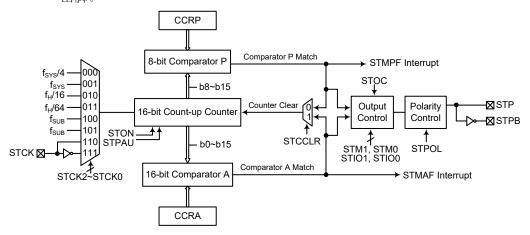

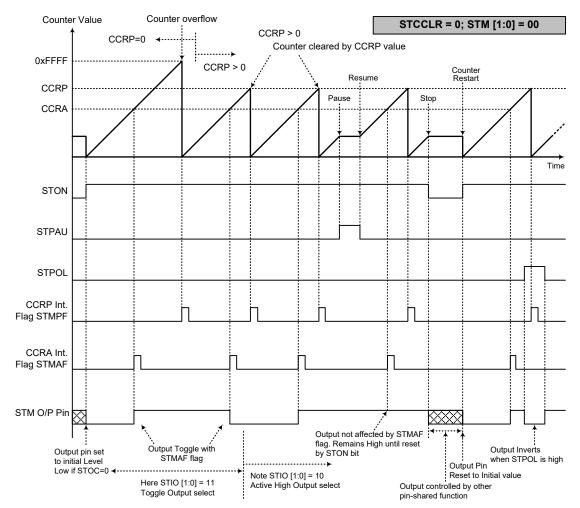

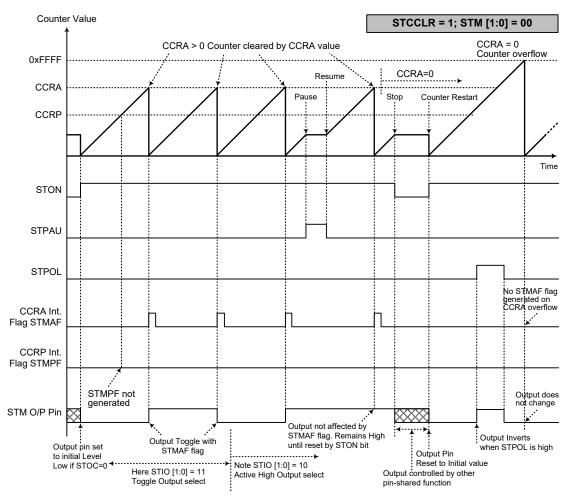

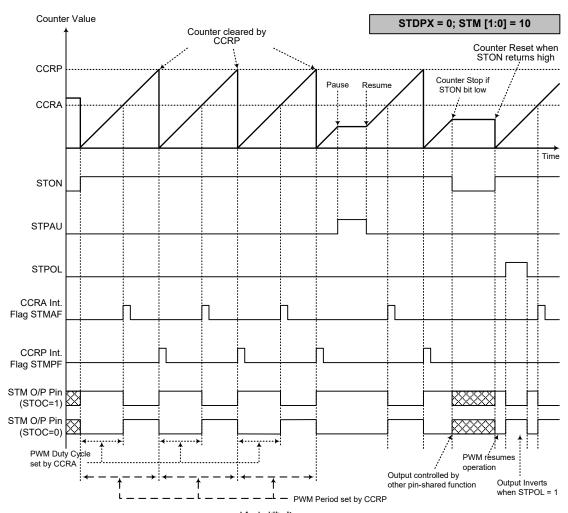

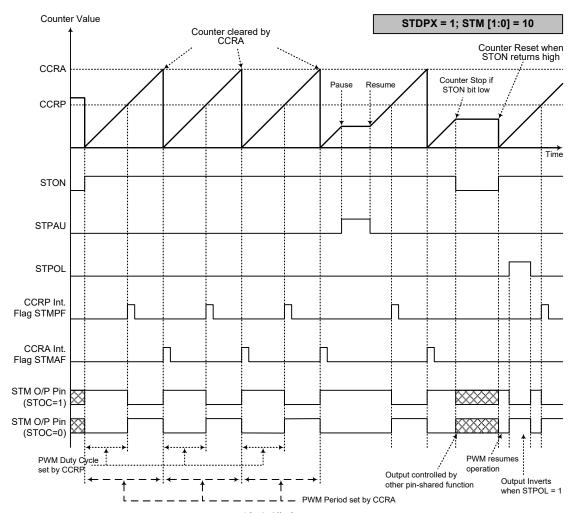

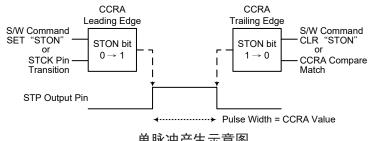

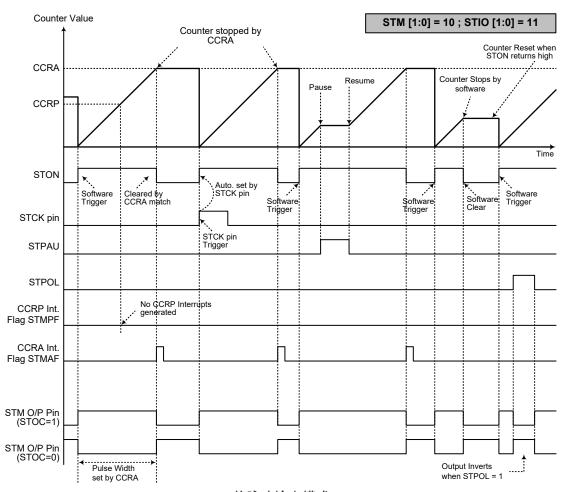

| 标准型 TM – STM       |     |

| 标准型 TM 操作          |     |

| 标准型 TM 寄存器介绍       |     |

| 标准型 TM 工作模式        | 103 |

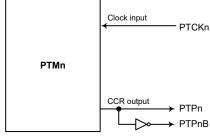

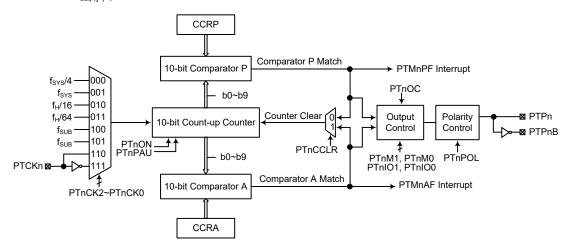

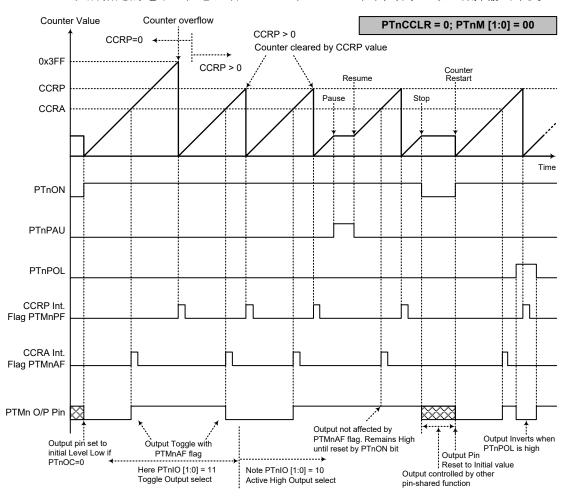

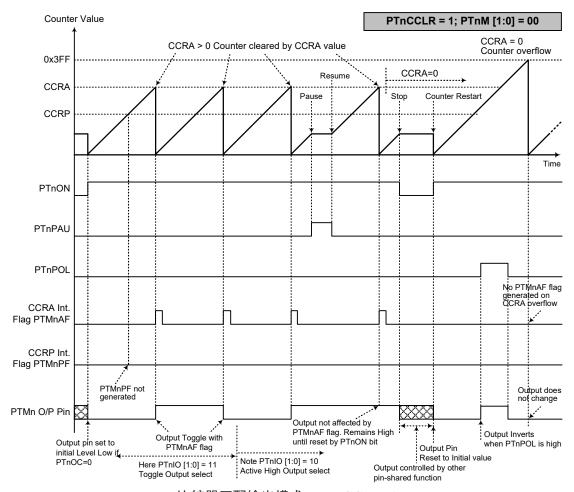

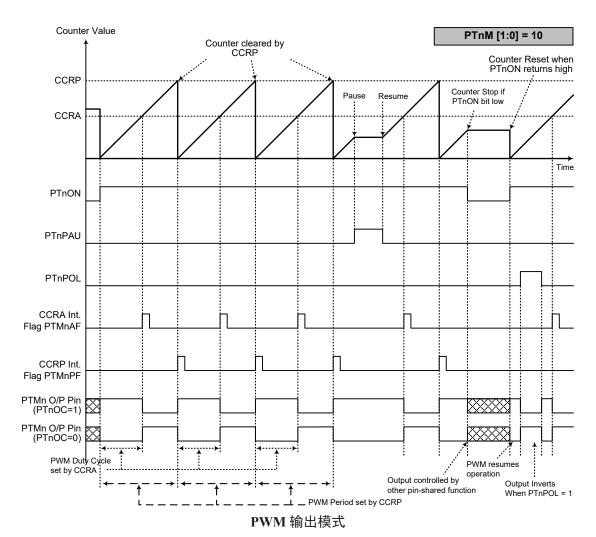

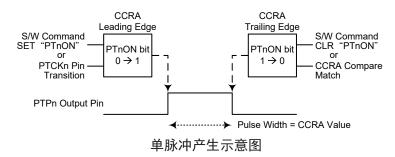

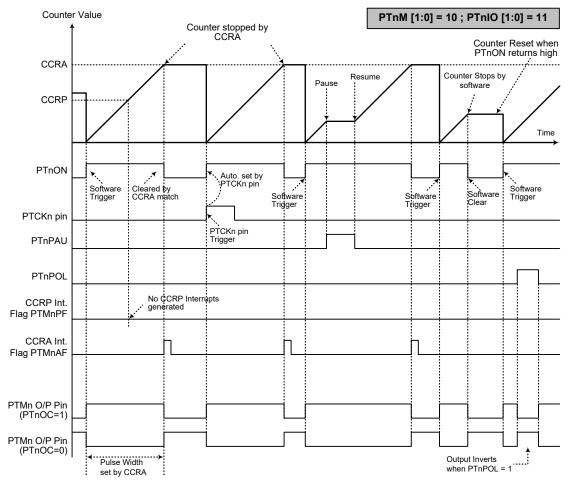

| 周期型 TM – PTM       | 110 |

| 周期型 TM 操作          |     |

| 周期型 TM 寄存器介绍       |     |

| 周期型 TM 工作模式        | 114 |

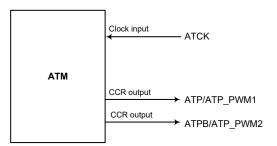

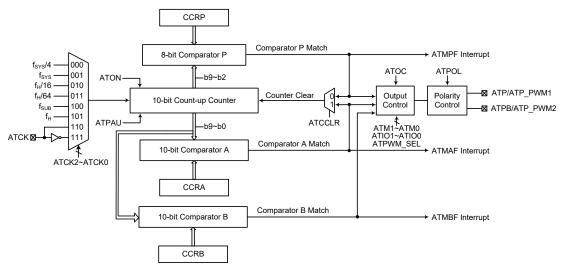

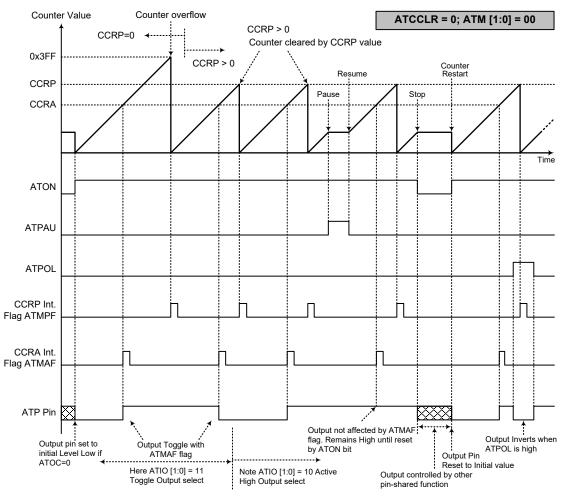

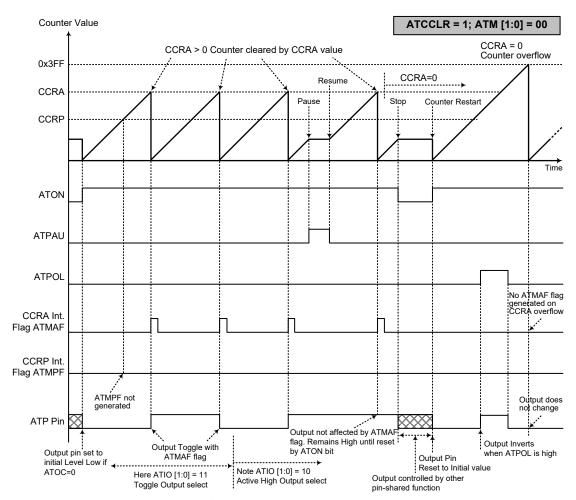

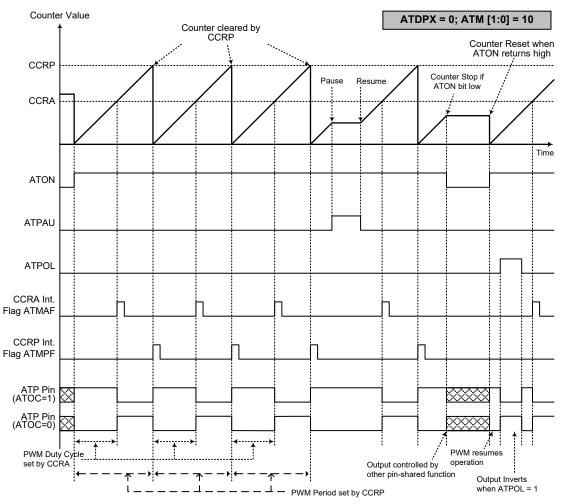

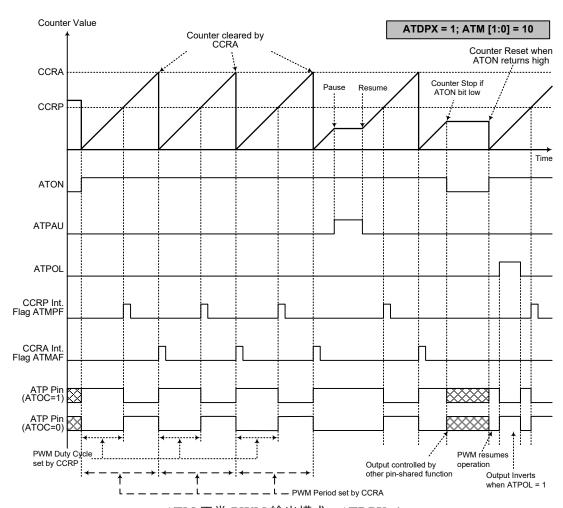

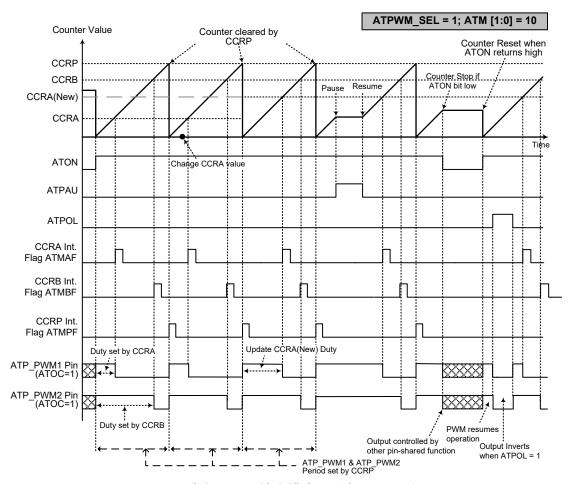

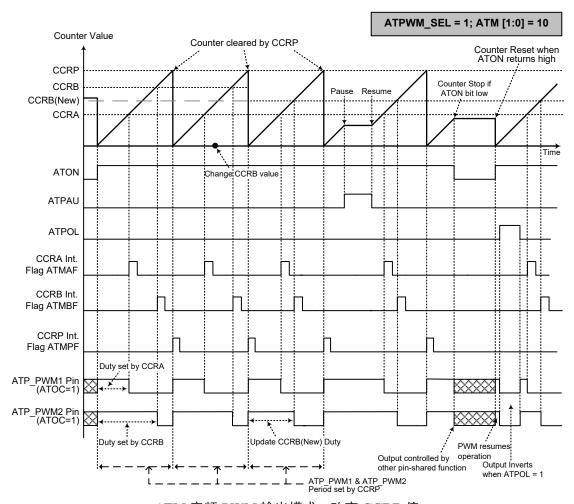

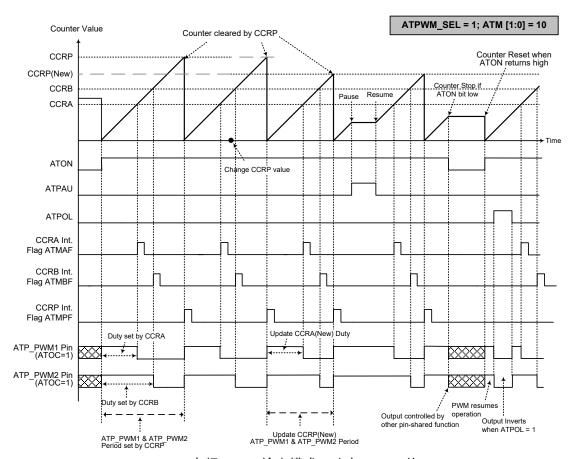

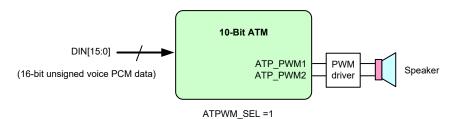

| 音频型 TM – ATM       | 121 |

| 音频型 TM 操作          | 121 |

| 音频型 TM 寄存器介绍       |     |

| 音频型 TM 工作模式        |     |

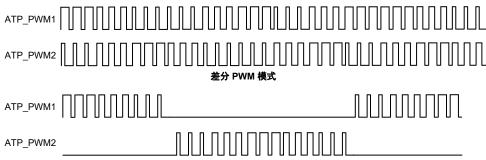

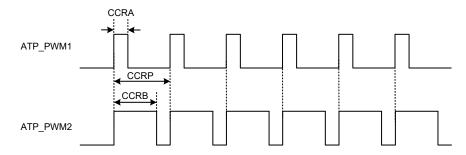

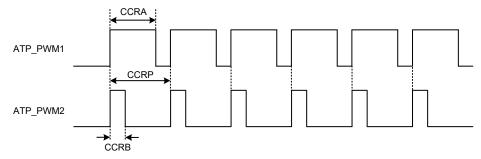

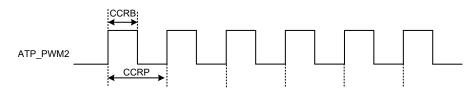

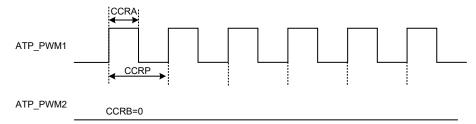

| 音频 PWM 输出使用介绍      | 135 |

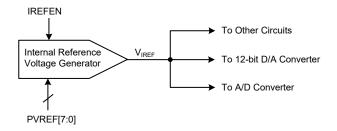

| 内部参考电压发生器          | 139 |

| 内部参考电压寄存器介绍        | 139 |

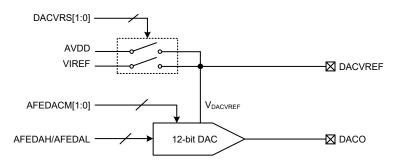

| D/A 转换器 – DAC      | 140 |

| D/A 转换器寄存器介绍       |     |

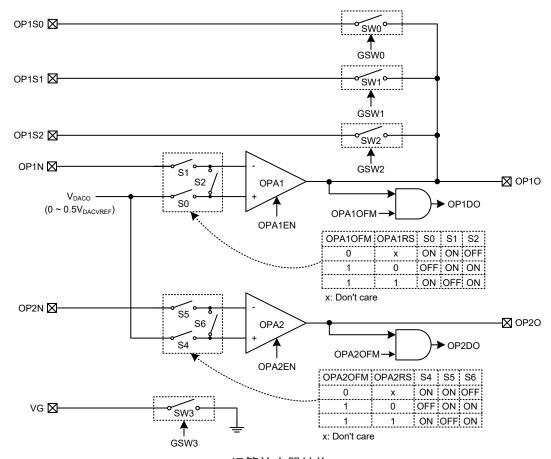

| 运算放大器 – <b>OPA</b> |     |

| OPA 寄存器介绍          |     |

| 输入失调校准             |     |

|                    |     |

| A/D 1<1大阳 - ADC                                                                                                                                                                                                                                 | 145               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

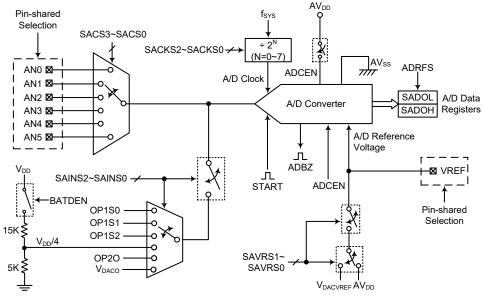

| A/D 转换器简介                                                                                                                                                                                                                                       | 145               |

| A/D 转换器寄存器介绍                                                                                                                                                                                                                                    | 146               |

| A/D 转换器操作                                                                                                                                                                                                                                       | 148               |

| A/D 转换器参考电压                                                                                                                                                                                                                                     | 148               |

| A/D 转换器输入信号                                                                                                                                                                                                                                     | 149               |

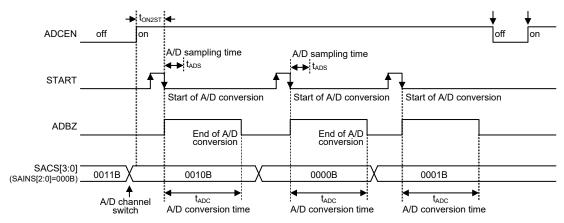

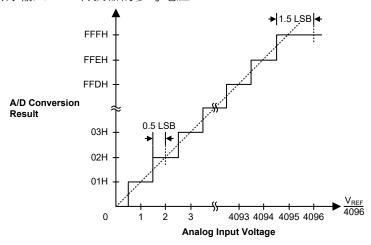

| A/D 转换率及时序图                                                                                                                                                                                                                                     | 149               |

| A/D 转换步骤                                                                                                                                                                                                                                        | 150               |

| 编程注意事项                                                                                                                                                                                                                                          | 151               |

| A/D 转换功能                                                                                                                                                                                                                                        | 151               |

| A/D 转换应用范例                                                                                                                                                                                                                                      | 151               |

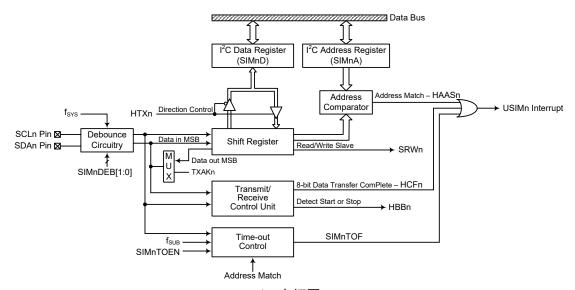

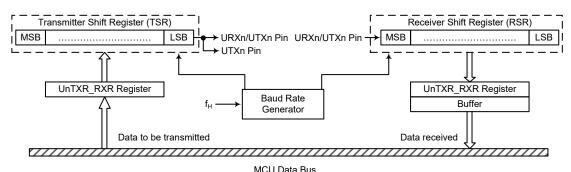

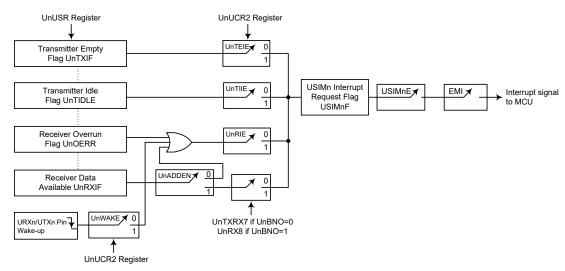

| 通用串行接口模块 – USIM                                                                                                                                                                                                                                 | 153               |

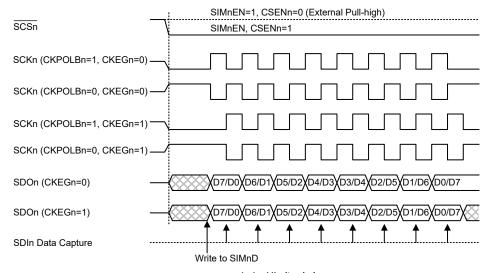

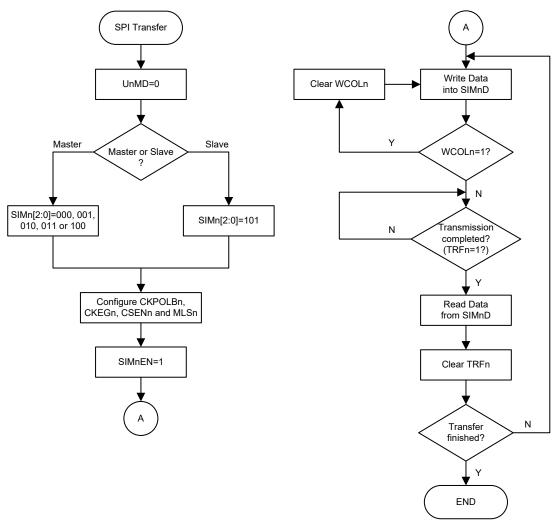

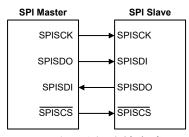

| SPI 接口                                                                                                                                                                                                                                          | 153               |

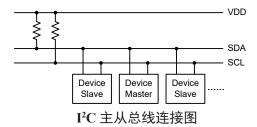

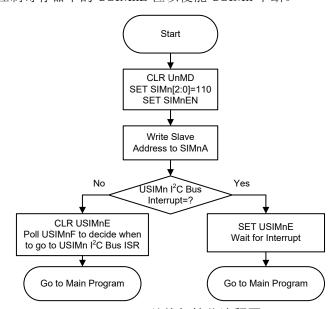

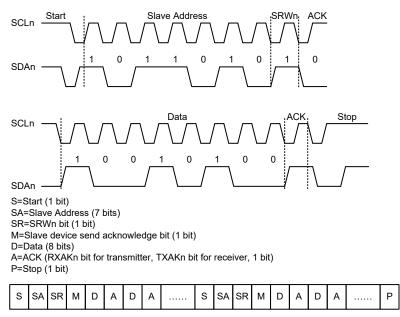

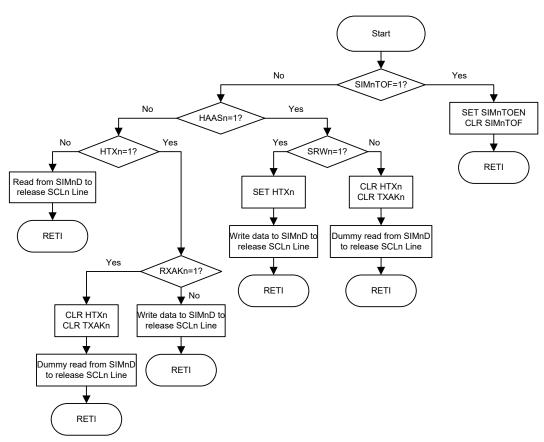

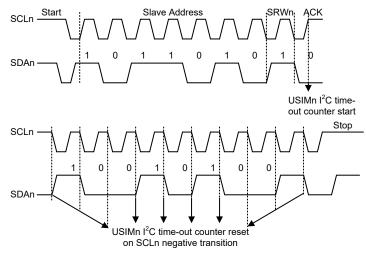

| I <sup>2</sup> C 接口                                                                                                                                                                                                                             | 160               |

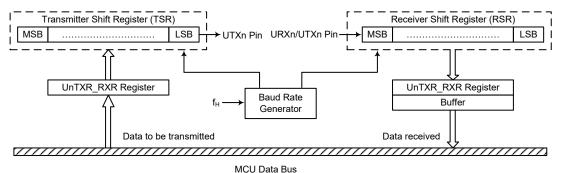

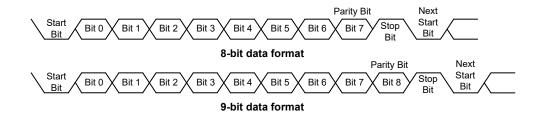

| UART 接口                                                                                                                                                                                                                                         | 169               |

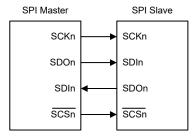

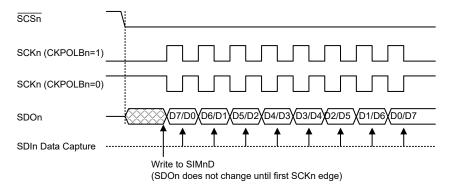

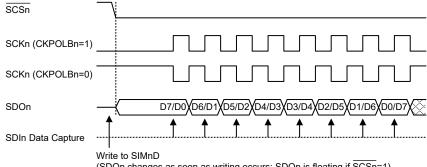

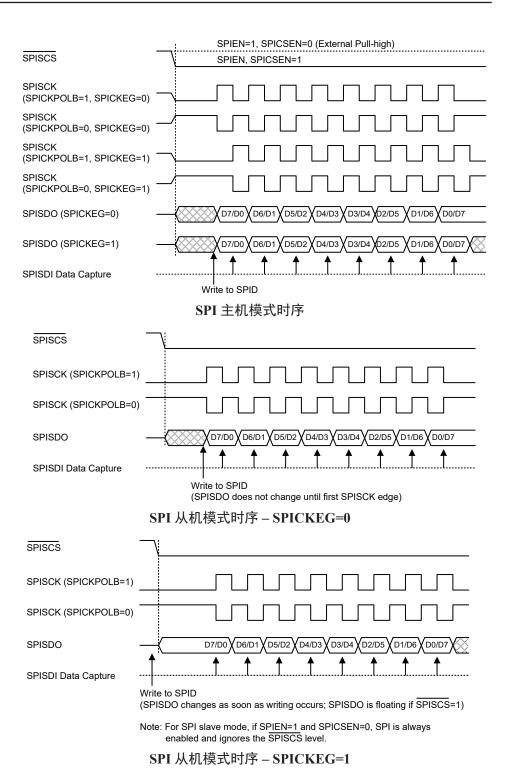

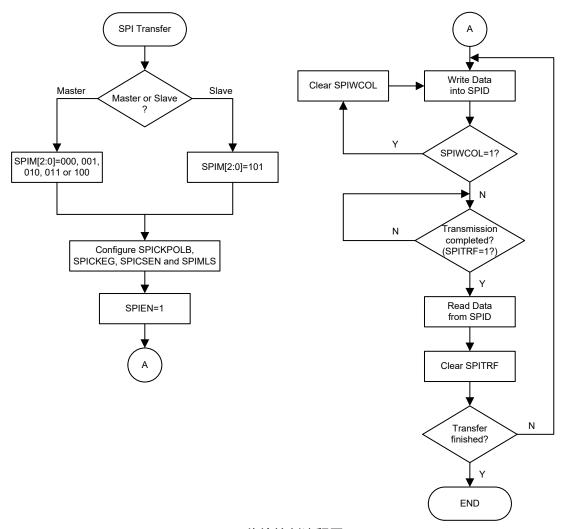

| SPI 串行接口                                                                                                                                                                                                                                        | 183               |

| SPI 接口操作                                                                                                                                                                                                                                        |                   |

| SPI 寄存器                                                                                                                                                                                                                                         |                   |

| SPI 通信                                                                                                                                                                                                                                          |                   |

| SPI 总线使能 / 除能                                                                                                                                                                                                                                   |                   |

| SPI 操作步骤                                                                                                                                                                                                                                        |                   |

| 错误侦测                                                                                                                                                                                                                                            |                   |

| LCD 驱动器                                                                                                                                                                                                                                         |                   |

|                                                                                                                                                                                                                                                 | ······ 170        |

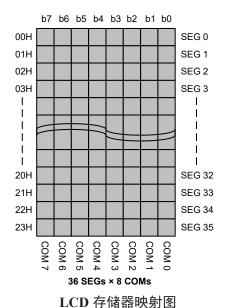

| LCD 显示数据存储器                                                                                                                                                                                                                                     | 190               |

| LCD 显示数据存储器                                                                                                                                                                                                                                     |                   |

| LCD 时钟源                                                                                                                                                                                                                                         | 191               |

| LCD 时钟源<br>LCD 寄存器介绍                                                                                                                                                                                                                            | 191<br>191        |

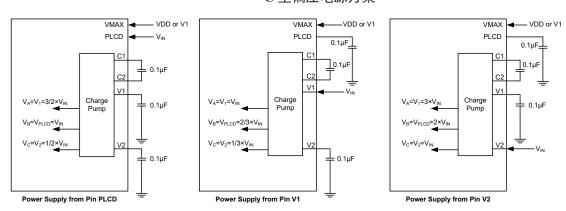

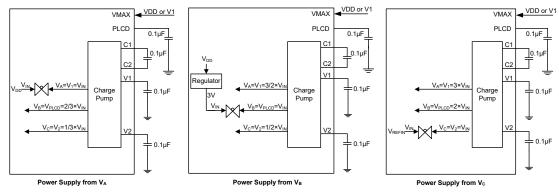

| LCD 时钟源<br>LCD 寄存器介绍<br>LCD 电压源和偏压                                                                                                                                                                                                              | 191<br>191<br>192 |

| LCD 时钟源<br>LCD 寄存器介绍<br>LCD 电压源和偏压<br>LCD 复位功能                                                                                                                                                                                                  |                   |

| LCD 时钟源                                                                                                                                                                                                                                         |                   |

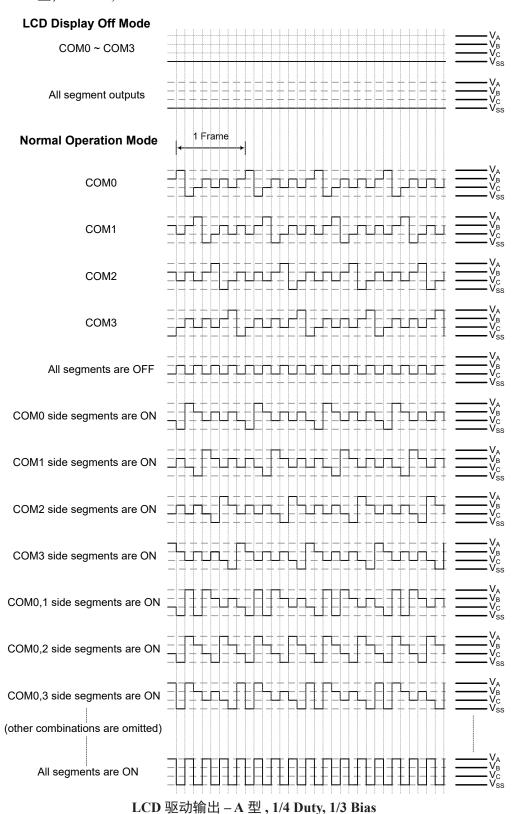

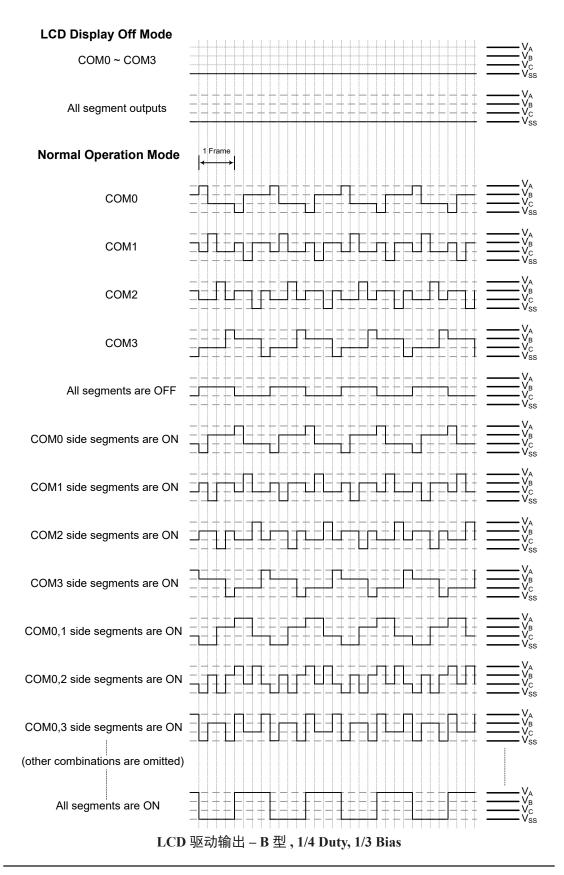

| LCD 时钟源         LCD 寄存器介绍         LCD 电压源和偏压         LCD 复位功能         LCD 驱动输出         编程注意事项                                                                                                                                                   |                   |

| LCD 时钟源         LCD 寄存器介绍         LCD 电压源和偏压         LCD 复位功能         LCD 驱动输出         编程注意事项                                                                                                                                                   |                   |

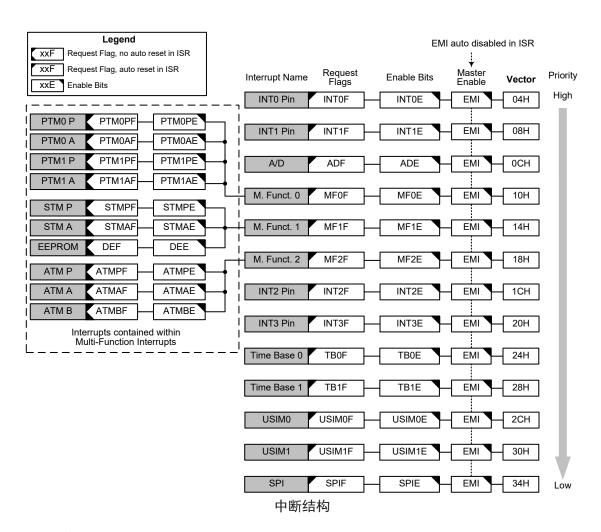

| LCD 时钟源         LCD 寄存器介绍         LCD 电压源和偏压         LCD 复位功能         LCD 驱动输出         编程注意事项         中断         中断寄存器                                                                                                                          |                   |

| LCD 时钟源         LCD 寄存器介绍         LCD 电压源和偏压         LCD 复位功能         LCD 驱动输出         编程注意事项         中断         中断条存器         中断操作                                                                                                             |                   |

| LCD 时钟源         LCD 寄存器介绍         LCD 电压源和偏压         LCD 复位功能         LCD 驱动输出         编程注意事项         中断         中断寄存器         中断操作         外部中断                                                                                                |                   |

| LCD 时钟源         LCD 寄存器介绍         LCD 电压源和偏压         LCD 复位功能         LCD 驱动输出         编程注意事项         中断         中断操作         外部中断         A/D 转换器中断                                                                                            |                   |

| LCD 时钟源         LCD 寄存器介绍         LCD 电压源和偏压         LCD 复位功能         LCD 驱动输出         编程注意事项         中断         中断操作         外部中断         A/D 转换器中断         多功能中断                                                                              |                   |

| LCD 时钟源         LCD 寄存器介绍         LCD 电压源和偏压         LCD 复位功能         LCD 驱动输出         编程注意事项         中断         中断寄存器         中断操作         外部中断         A/D 转换器中断         多功能中断         TM 中断                                                  |                   |

| LCD 时钟源         LCD 寄存器介绍         LCD 电压源和偏压         LCD 复位功能         LCD 驱动输出         编程注意事项         中断         中断条存器         中断操作         外部中断         A/D 转换器中断         多功能中断         TM 中断         EEPROM 中断                                |                   |

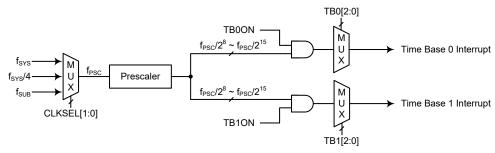

| LCD 时钟源         LCD 寄存器介绍         LCD 电压源和偏压         LCD 复位功能         LCD 驱动输出         编程注意事项         中断         中断操作         外部中断         A/D 转换器中断         多功能中断         TM 中断         EEPROM 中断         时基中断                                 |                   |

| LCD 时钟源         LCD 寄存器介绍         LCD 电压源和偏压         LCD 复位功能         LCD 驱动输出         编程注意事项         中断         中断寄存器         中断操作         外部中断         A/D 转换器中断         多功能中断         TM 中断         EEPROM 中断         时基中断         通用串行接口中断  |                   |

| LCD 时钟源 LCD 寄存器介绍 LCD 电压源和偏压 LCD 复位功能 LCD 驱动输出 编程注意事项 中断 中断条存器 中断操作 外部中断 A/D 转换器中断 多功能中断 TM 中断 EEPROM 中断 时基中断 明基中断 到用串行接口中断 SPI 接口中断                                                                                                            |                   |

| LCD 时钟源         LCD 寄存器介绍         LCD 电压源和偏压         LCD 复位功能         LCD 驱动输出         编程注意事项         中断         中断操作         外部中断         A/D 转换器中断         多功能中断         TM 中断         EEPROM 中断         时基中断         通用串行接口中断         P的唤醒功能 |                   |

| LCD 时钟源 LCD 寄存器介绍 LCD 电压源和偏压 LCD 复位功能 LCD 驱动输出 编程注意事项 中断 中断条存器 中断操作 外部中断 A/D 转换器中断 多功能中断 TM 中断 EEPROM 中断 时基中断 明基中断 到用串行接口中断 SPI 接口中断                                                                                                            |                   |

| 应用电路                         | 213 |

|------------------------------|-----|

| 指令集                          | 214 |

|                              | 214 |

| 指令周期                         |     |

| 数据的传送                        | 214 |

| 算术运算                         | 214 |

| 逻辑和移位运算                      | 214 |

| 分支和控制转换                      | 215 |

| 位运算                          | 215 |

| 查表运算                         | 215 |

| 其它运算                         | 215 |

| 指令集概要                        | 216 |

| 惯例                           |     |

| 扩展指令集                        | 219 |

| 指令定义                         | 221 |

| 扩展指令定义                       |     |

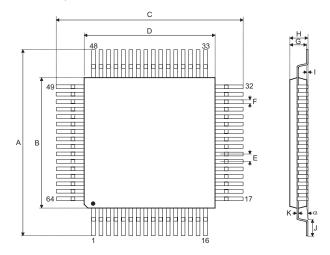

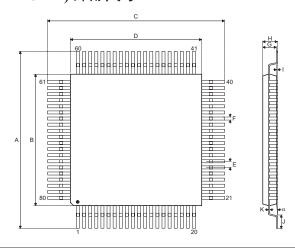

| 封装信息                         | 243 |

| 64-pin LQFP (7mm×7mm) 外形尺寸   |     |

| 80-pin LOFP (10mm×10mm) 外形尺寸 | 245 |

6

#### 特性

#### CPU 特性

- 工作电压:

- ♦ f<sub>SYS</sub>=4MHz: 2.2V~5.5V

- $f_{SYS}=8MHz$ : 2.2V~5.5V

- $f_{SYS}=12MHz$ : 2.7V~5.5V

- ♦  $f_{SYS} = 16MHz$ : 3.3V~5.5V

- V<sub>DD</sub>=5V, 系统时钟为 16MHz 时, 指令周期为 0.25μs

- 暂停和唤醒功能, 以降低功耗

- 振荡器类型:

- ◆ 内部高速 4/8/12MHz RC HIRC

- ◆ 内部低速 32kHz RC LIRC

- ◆ 外部高速晶振 HXT

- ◆ 外部低速 32.768kHz 晶振 LXT

- 完全集成的内部振荡器无需外接元器件

- 多种工作模式: 快速模式、低速模式、空闲模式和休眠模式

- 所有指令都可在 1~3 个指令周期内完成

- 查表指令

- 115 条功能强大的指令系统

- 16 层硬件堆栈

- 位操作指令

#### 周边特性

- Flash 程序存储器: 32K×16

- 数据存储器: 2048×8

- True EEPROM 存储器: 2048×8

- 在线应用编程功能 IAP

- 支持片上调试功能 OCDS

- 看门狗定时器功能

- 58 个双向 I/O 口

- 4 个与 I/O 口共用引脚的外部中断输入

- 多个定时器模块用于时间测量、比较匹配输出、PWM 输出及单脉冲输出

- 双时基功能,用于产生固定时间的中断信号

- 血糖仪 AFE 集成电路

- ♦ 6 个外部通道的 12-bit 分辨精度 A/D 转换器

- ◆ 内部参考电压发生器

- ◆ 12-bit D/A 转换器

- ◆ 2 个运算放大器

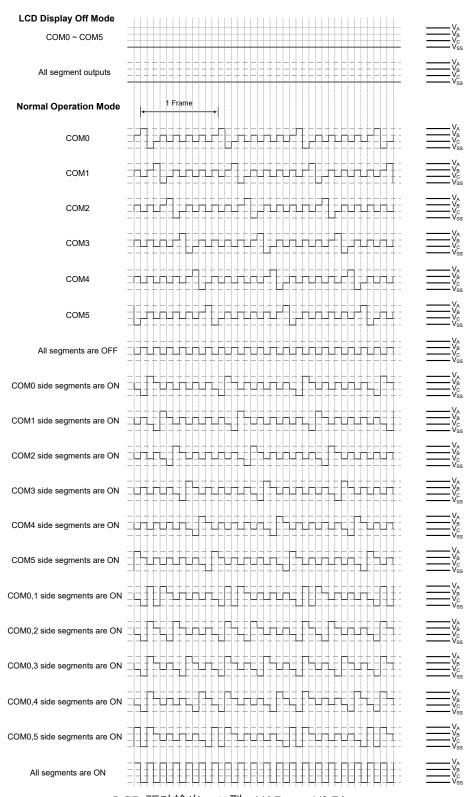

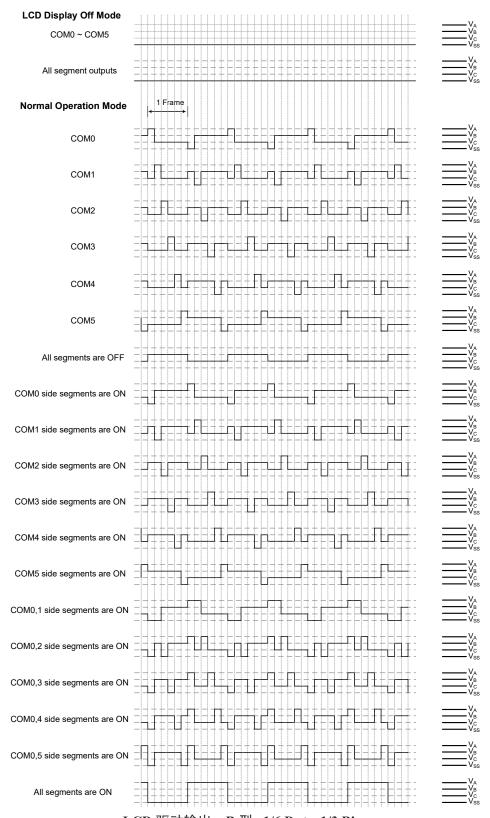

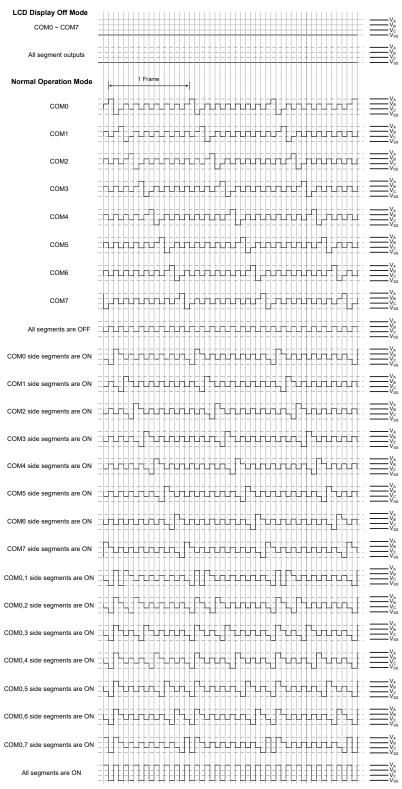

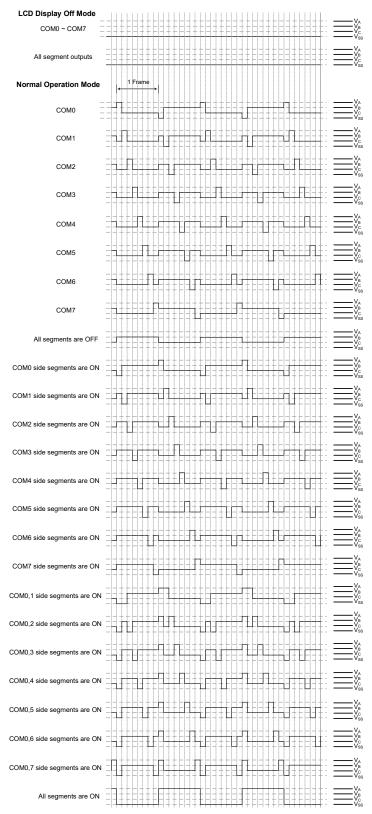

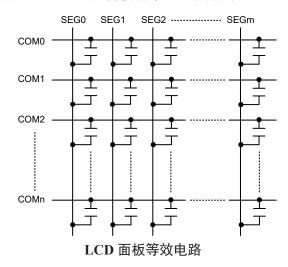

- LCD 驱动器功能

- ◆ SEG × COM: 36×4, 34×6 或 32×8

- ◆ 占空比类型: 1/4 Duty, 1/6 Duty 或 1/8 Duty

- ♦ 偏压电平: 1/3 bias

- ◆ 偏压类型: C型

- ◆ 波形类型: A 型或 B 型

- 两组通用串行接口模块 USIM, 用于 SPI, I2C 和 UART 通信

- 单个独立的串行外设接口 SPI

- 低电压复位功能

- 封装类型: 64/80-pin LQFP

### 开发工具

为加快产品开发并简化单片机参数设置,Holtekt 提供相关开发工具,用户可通过以下链接下载:

https://www.holtek.com.cn/esk-fv160-200

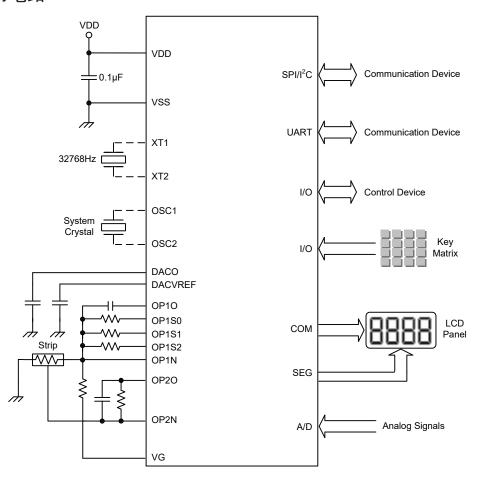

## 概述

该单片机是一款具有 8 位高性能精简指令集的 Flash 单片机,内置血糖仪模拟前端处理模块和 LCD 驱动器,专门为带 LCD 显示的血糖仪产品而设计。

在存储器特性方面,Flash 存储器可多次编程的特性给用户提供了较大的方便。此外还包括 RAM 数据存储器和用于存储序列数据、校准数据等非易失性数据的 True EEPROM 存储器。此外通过使用 IAP 功能,便于用户直接将测量的数据存储至程序存储器中或进行应用程序更新。

在模拟特性方面,该单片机包含一个多通道 12-bit A/D 转换器、一个 12-bit D/A 转换器和两个内部运算放大器。其具有多个使用灵活的定时器模块,可提供定时功能、脉冲产生功能及 PWM 产生功能。内建完整的 SPI、UART 和 I<sup>2</sup>C 接口功能,为设计者提供了一个易与外部硬件通信的接口。内部看门狗定时器和低电压复位等内部保护特性,外加优秀的抗干扰和 ESD 保护性能,确保单片机在恶劣的电磁干扰环境下可靠地运行。

该单片机提供了丰富的内部和外部,高速和低速振荡器功能选项。内部振荡器完全内建,无需外围元器件。其在不同工作模式之间动态切换的能力,为用户提供了一个优化单片机操作和减少功耗的手段。

针对血糖仪应用,该单片机内置多个相关功能,例如内部参考电压发生器、12-bit D/A转换器、LCD驱动功能等。外加I/O使用灵活和时基功能等其它特性,使这款单片机可提供多个方案应用于带有LCD显示的血糖仪产品。

Rev.1.21 8 2021-11-01

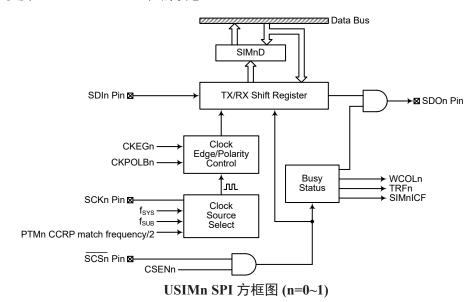

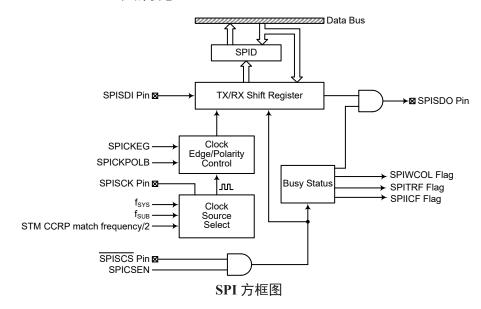

## 方框图

## 引脚图

Rev.1.21 10 2021-11-01

- 注: 1. 若共用脚同时有多种输出,所需引脚共用功能通过相应的软件控制位决定。

- 2. 在较小封装中可能含有未引出的引脚,需合理设置其状态以避免输入浮空造成额外耗电,详见"待机电流注意事项"和"输入/输出端口"章节。

## 引脚说明

该单片机每个引脚的功能如下表所述,而引脚配置的详细内容见规格书其它章节。下述引脚功能表格是针对最大封装提供的引脚,对于小封装会有部分引脚未出现。

| 引脚名称             | 功能           | OPT                    | I/T | O/T  | 说明                             |

|------------------|--------------|------------------------|-----|------|--------------------------------|

| PA0/OCDSDA/      | PA0          | PAPU<br>PAWU           | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻和唤醒功能 |

| ICPDA            | OCDSDA       | _                      | ST  | CMOS | OCDS 数据 / 地址引脚                 |

|                  | ICPDA        | _                      | ST  | CMOS | ICP 数据 / 地址引脚                  |

| PA1/SCS0         | PA1          | PAPU<br>PAWU<br>PAS0   | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻和唤醒功能 |

|                  | SCS0         | PAS0                   | ST  | CMOS | USIM0 SPI 从机选择                 |

| PA2/OCDSCK/      | PA2          | PAPU<br>PAWU           | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻和唤醒功能 |

| ICPCK            | OCDSCK       | _                      | ST  | _    | OCDS 时钟引脚                      |

|                  | ICPCK        |                        | ST  |      | ICP 时钟引脚                       |

| PA3/SCK0/SCL0    | PA3          | PAPU<br>PAWU<br>PAS0   | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻和唤醒功能 |

|                  | SCK0         | PAS0                   | ST  | CMOS | USIM0 SPI 串行时钟                 |

|                  | SCL0         | PAS0                   | ST  | NMOS | USIM0 I <sup>2</sup> C 时钟线     |

| PA4/ATPB/        | PA4          | PAPU<br>PAWU<br>PAS1   | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻和唤醒功能 |

| ATP_PWM2         | ATPB         | PAS1                   |     | CMOS | ATM 反相输出                       |

| _                | ATP_<br>PWM2 | PAS1                   | _   | CMOS | ATM 音频 PWM 输出模式输出 2            |

| DAS/ATD/ATD DWAM | PA5          | PAPU<br>PAWU<br>PAS1   | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻和唤醒功能 |

| PA5/ATP/ATP_PWM1 | ATP          | PAS1                   | _   | CMOS | ATM 输出                         |

|                  | ATP_<br>PWM1 | PAS1                   |     | CMOS | ATM 音频 PWM 输出模式输出 1            |

|                  | PA6          | PAPU<br>PAWU<br>PAS1   | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻和唤醒功能 |

| PA6/VG/INT0      | VG           | PAS1                   | AN  | _    | 虚拟地                            |

|                  | INT0         | PAS1<br>INTEG<br>INTC0 | ST  | _    | 外部中断输入                         |

Rev.1.21 12 2021-11-01

| 引脚名称                   | 功能            | OPT                    | I/T                       | O/T  | 说明                                                   |

|------------------------|---------------|------------------------|---------------------------|------|------------------------------------------------------|

|                        | PA7           | PAPU<br>PAWU<br>PAS1   | ST                        | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻和唤醒功能                       |

| PA7/OP2N/INT1          | OP2N          | PAS1                   | AN                        |      | OPA2 负输入端外部输入                                        |

|                        | INT1          | PAS1<br>INTEG<br>INTC0 | ST                        | _    | 外部中断输入                                               |

| PB0/OP2O               | PB0           | PBPU<br>PBS0           | ST                        | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻                            |

|                        | OP2O          | PBS0                   | _                         | AN   | OPA2 输出                                              |

| PB1/OP1N               | PB1           | PBPU<br>PBS0           | ST                        | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻                            |

|                        | OP1N          | PBS0                   | AN                        |      | OPA1 负输入端外部输入                                        |

| PB2/AN0                | PB2           | PBPU<br>PBS0           | ST                        | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻                            |

|                        | AN0           | PBS0                   | AN                        | _    | A/D 转换器外部输入通道                                        |

| PB3/AN1                | PB3           | PBPU<br>PBS0           | ST                        | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻                            |

|                        | AN1           | PBS0                   | AN                        | _    | A/D 转换器外部输入通道                                        |

| DD 4/DTD0/4340         | PB4           | PBPU<br>PBS1           | ST                        | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻                            |

| PB4/PTP0/AN2           | PTP0          | PBS1                   | _                         | CMOS | PTM0 输出                                              |

|                        | AN2           | PBS1                   | AN                        | _    | A/D 转换器外部输入通道                                        |

| DD 5 /DTDOD / A N/2    | PBSI          | CMOS                   | 通用 I/O 口,可通过寄存器设置上<br>拉电阻 |      |                                                      |

| PB5/PTP0B/AN3          | PTP0B         | PBS1                   | _                         | CMOS | PTM0 反相输出                                            |

|                        | AN3           | PBS1                   | AN                        |      | A/D 转换器外部输入通道                                        |

| DD (/43)4/// IDEE/     | PB6           | PBPU<br>PBS1           | ST                        | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻                            |

| PB6/AN4/VREF/<br>VDDIO | AN4           | PBS1                   | AN                        | _    | A/D 转换器外部输入通道                                        |

| VDDIO                  | VREF          | PBS1                   | AN                        | _    | A/D 转换器外部参考电压输入                                      |

|                        | VDDIO         | PBS1                   | PWR                       |      | PD0~PD3 引脚电源                                         |

| DDG/ANG/GGW1/          | PB7           | PBPU<br>PBS1           | ST                        | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻                            |

| PB7/AN5/SCK1/<br>SCL1  | SCK1          | PBS1                   | ST                        | CMOS | USIM1 SPI 串行时钟                                       |

| BCLI                   | SCL1          | PBS1                   | ST                        | NMOS | USIM1 I <sup>2</sup> C 时钟线                           |

|                        | AN5           | PBS1                   | AN                        |      | A/D 转换器外部输入通道                                        |

|                        | PC0           | PCPU<br>PCS0           | ST                        | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻                            |

| PC0/SDI0/SDA0/         | SDI0          | PCS0                   | ST                        | _    | USIM0 SPI 串行数据输入                                     |

| URX0/UTX0              | SDA0          | PCS0                   | ST                        | NMOS | USIM0 I <sup>2</sup> C 数据线                           |

|                        | URX0/<br>UTX0 | PCS0                   | ST                        | CMOS | USIMO UART 串行数据输入(全双工通信); UART 串行数据输入/<br>输出(单线通信模式) |

| 引脚名称                     | 功能            | OPT                    | I/T | O/T  | 说明                                               |

|--------------------------|---------------|------------------------|-----|------|--------------------------------------------------|

|                          | PC1           | PCPU<br>PCS0           | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻                        |

| PC1/INT3/SDI1/           | INT3          | PCS0<br>INTEG<br>INTC2 | ST  | _    | 外部中断输入                                           |

| SDA1/URX1/UTX1           | SDI1          | PCS0                   | ST  | _    | USIM1 SPI 串行数据输入                                 |

|                          | SDA1          | PCS0                   | ST  | NMOS | USIM1 I <sup>2</sup> C 数据线                       |

|                          | URX1/<br>UTX1 | PCS0                   | ST  | CMOS | USIM1 UART 串行数据输入(全双工通信); UART 串行数据输入/输出(单线通信模式) |

|                          | PC2           | PCPU<br>PCS0           | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻                        |

| PC2/INT2/SDO1/<br>UTX1   | INT2          | PCS0<br>INTEG<br>INTC1 | ST  | _    | 外部中断输入                                           |

|                          | SDO1          | PCS0                   | _   | CMOS | USIM1 SPI 串行数据输出                                 |

|                          | UTX1          | PCS0                   | _   | CMOS | USIM1 UART 串行数据输出                                |

| PC3/XT1                  | PC3           | PCPU<br>PCS0           | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻                        |

|                          | XT1           | PCS0                   | LXT | _    | LXT 振荡器引脚                                        |

| PC4/XT2                  | PC4           | PCPU<br>PCS1           | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻                        |

|                          | XT2           | PCS1                   | _   | LXT  | LXT 振荡器引脚                                        |

| PC5/SCS1/ATCK            | PC5           | PCPU<br>PCS1           | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻                        |

| PC5/SCS1/ATCK            | SCS1          | PCS1                   | ST  | CMOS | USIM1 SPI 从机选择                                   |

|                          | ATCK          | PCS1                   | ST  | _    | ATM 时钟输入                                         |

| DGC/GD OO/LITTYO         | PC6           | PCPU<br>PCS1           | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻                        |

| PC6/SDO0/UTX0            | SDO0          | PCS1                   | _   | CMOS | USIM0 SPI 串行数据输出                                 |

|                          | UTX0          | PCS1                   | _   | CMOS | USIM0 UART 串行数据输出                                |

|                          | PD0           | PDPU<br>PDS0           | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻                        |

| PD0/SEG0/PTP0/<br>SPISCK | SEG0          | PDS0                   | _   | AN   | LCD SEG 信号输出                                     |

| SPISCK                   | PTP0          | PDS0                   | _   | CMOS | PTM0 输出                                          |

|                          | SPISCK        | PDS0                   | ST  | CMOS | SPI 串行时钟                                         |

| DD 1/0F G1/DTD 05 /      | PD1           | PDPU<br>PDS0           | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻                        |

| PD1/SEG1/PTP0B/          | SEG1          | PDS0                   |     | AN   | LCD SEG 信号输出                                     |

| SPISDI                   | PTP0B         | PDS0                   | _   | CMOS | PTM0 反相输出                                        |

|                          | SPISDI        | PDS0                   | ST  | _    | SPI 串行数据输入                                       |

| 引脚名称                      | 功能           | OPT          | I/T | O/T  | 说明                        |

|---------------------------|--------------|--------------|-----|------|---------------------------|

|                           | PD2          | PDPU<br>PDS0 | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻 |

| PD2/SEG2/PTCK0/<br>SPISDO | SEG2         | PDS0         | _   | AN   | LCD SEG 信号输出              |

| 381300                    | PTCK0        | PDS0         | ST  | _    | PTM0 时钟输入                 |

|                           | SPISDO       | PDS0         | _   | CMOS | SPI 串行数据输出                |

| ND2/GEG2/GNIGGG           | PD3          | PDPU<br>PDS0 | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻 |

| PD3/SEG3/SPISCS           | SEG3         | PDS0         | _   | AN   | LCD SEG 信号输出              |

|                           | SPISCS       | PDS0         | ST  | CMOS | SPI 从机选择                  |

|                           | PD4          | PDPU<br>PDS1 | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻 |

| PD4/SEG4/ATP/             | SEG4         | PDS1         | _   | AN   | LCD SEG 信号输出              |

| ATP_PWM1                  | ATP          | PDS1         | _   | CMOS | ATM 输出                    |

|                           | ATP_<br>PWM1 | PDS1         | _   | CMOS | ATM 音频 PWM 输出模式输出 1       |

|                           | PD5          | PDPU<br>PDS1 | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻 |

| PD5/SEG5/ATPB/            | SEG5         | PDS1         | _   | AN   | LCD SEG 信号输出              |

| ATP_PWM2                  | ATPB         | PDS1         | _   | CMOS | ATM 反相输出                  |

|                           | ATP_<br>PWM2 | PDS1         | _   | CMOS | ATM 音频 PWM 输出模式输出 2       |

| ND ( long) land           | PD6          | PDPU<br>PDS1 | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻 |

| PD6/OSC1/SEG6             | OSC1         | PDS1         | HXT | _    | HXT 振荡器引脚                 |

|                           | SEG6         | PDS1         | _   | AN   | LCD SEG 信号输出              |

| PD7/00C0/GE07             | PD7          | PDPU<br>PDS1 | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻 |

| PD7/OSC2/SEG7             | OSC2         | PDS1         | _   | HXT  | HXT 振荡器引脚                 |

|                           | SEG7         | PDS1         | _   | AN   | LCD SEG 信号输出              |

| DEO/GEGO/GTD              | PE0          | PEPU<br>PES0 | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻 |

| PE0/SEG8/STP              | SEG8         | PES0         | _   | AN   | LCD SEG 信号输出              |

|                           | STP          | PES0         | _   | CMOS | STM 输出                    |

| DE1/GEGO/GEDD             | PE1          | PEPU<br>PES0 | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻 |

| PE1/SEG9/STPB             | SEG9         | PES0         |     | AN   | LCD SEG 信号输出              |

|                           | STPB         | PES0         | _   | CMOS | STM 反相输出                  |

| DE2/SEC10/STCV            | PE2          | PEPU<br>PES0 | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻 |

| PE2/SEG10/STCK            | SEG10        | PES0         | _   | AN   | LCD SEG 信号输出              |

|                           | STCK         | PES0         | ST  | _    | STM 时钟输入                  |

| DE2/SEC11/DTD1            | PE3          | PEPU<br>PES0 | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻 |

| PE3/SEG11/PTP1            | SEG11        | PES0         | _   | AN   | LCD SEG 信号输出              |

|                           | PTP1         | PES0         | _   | CMOS | PTM1 输出                   |

| 引脚名称                    | 功能       | OPT          | I/T | O/T  | 说明                        |

|-------------------------|----------|--------------|-----|------|---------------------------|

| DE A/GE G12/DED1D       | PE4      | PEPU<br>PES1 | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻 |

| PE4/SEG12/PTP1B         | SEG12    | PES1         |     | AN   | LCD SEG 信号输出              |

|                         | PTP1B    | PES1         | _   | CMOS | PTM1 反相输出                 |

| DES/CEC12/DTCV1         | PE5      | PEPU<br>PES1 | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻 |

| PE5/SEG13/PTCK1         | SEG13    | PES1         | _   | AN   | LCD SEG 信号输出              |

|                         | PTCK1    | PES1         | ST  | _    | PTM1 时钟输入                 |

| PE6/SEG14               | PE6      | PEPU<br>PES1 | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻 |

|                         | SEG14    | PES1         | _   | AN   | LCD SEG 信号输出              |

| PE7/SEG15               | PE7      | PEPU<br>PES1 | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻 |

|                         | SEG15    | PES1         | _   | AN   | LCD SEG 信号输出              |

| PF0/SEG16~<br>PF3/SEG19 | PF0~3    | PFPU<br>PFS0 | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻 |

| FF5/SEG19               | SEG16~19 | PFS0         |     | AN   | LCD SEG 信号输出              |

| PF4/SEG20~<br>PF7/SEG23 | PF4~7    | PFPU<br>PFS1 | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻 |

| PF //SEG23              | SEG20~23 | PFS1         | _   | AN   | LCD SEG 信号输出              |

| PG0/SEG24~<br>PG3/SEG27 | PG0~3    | PGPU<br>PGS0 | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻 |

| T G5/SEG27              | SEG24~27 | PGS0         | _   | AN   | LCD SEG 信号输出              |

| DC4/COM7/SEC29          | PG4      | PGPU<br>PGS1 | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻 |

| PG4/COM7/SEG28          | COM7     | PGS1         | _   | AN   | LCD COM 信号输出              |

|                         | SEG28    | PGS1         | _   | AN   | LCD SEG 信号输出              |

| PG5/COM6/SEG29          | PG5      | PGPU<br>PGS1 | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻 |

| PG3/COM0/SEG29          | COM6     | PGS1         | _   | AN   | LCD COM 信号输出              |

|                         | SEG29    | PGS1         |     | AN   | LCD SEG 信号输出              |

| PH2/CLO                 | PH2      | PHPU<br>PHS0 | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻 |

|                         | CLO      | PHS0         |     | CMOS | 系统时钟输出                    |

| PH3/SEG32               | PH3      | PHPU<br>PHS0 | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻 |

|                         | SEG32    | PHS0         | _   | AN   | LCD SEG 信号输出              |

| PH4/SEG33~<br>PH6/SEG35 | PH4~6    | PHPU<br>PHS1 | ST  | CMOS | 通用 I/O 口,可通过寄存器设置上<br>拉电阻 |

|                         | SEG33~35 | PHS1         |     | AN   | LCD SEG 信号输出              |

| COM0~COM3               | COM0~3   |              |     | AN   | LCD COM 信号输出              |

| COM4/SEG31              | COM4     | COMS         | _   | AN   | LCD COM 信号输出              |

|                         | SEG31    | COMS         |     | AN   | LCD SEG 信号输出              |

| COM5/SEG30              | COM5     | COMS         | _   | AN   | LCD COM 信号输出              |

|                         | SEG30    | COMS         | _   | AN   | LCD SEG 信号输出              |

| 引脚名称    | 功能      | OPT | I/T | O/T | 说明                        |

|---------|---------|-----|-----|-----|---------------------------|

| VMAX    | VMAX    | _   | PWR | _   | LCD 最大电压,需连接到 VDD 或<br>V1 |

| PLCD    | PLCD    |     | PWR | AN  | LCD 电源输入                  |

| V1      | V1      | _   | PWR | AN  | LCD 电压泵                   |

| V2      | V2      | _   | PWR | AN  | LCD 电压泵                   |

| C1      | V1      | _   | PWR | AN  | LCD 电压泵                   |

| C2      | V2      | _   | PWR | AN  | LCD 电压泵                   |

| OP1S0   | OP1S0   | _   | _   | AN  | OPA1 输出 0,通过模拟开关控制        |

| OP1S1   | OP1S1   | _   | _   | AN  | OPA1 输出 1,通过模拟开关控制        |

| OP1S2   | OP1S2   | _   | _   | AN  | OPA1 输出 2, 通过模拟开关控制       |

| OP1O    | OP1O    | _   | _   | AN  | OPA1 输出                   |

| DACVREF | DACVREF | _   | _   | AN  | D/A 转换器参考电压               |

| DACO    | DACO    | _   | _   | AN  | D/A 转换器输出                 |

| VDD     | VDD     | _   | PWR |     | 数字正电源                     |

| VSS     | VSS     | _   | PWR | _   | 数字负电源                     |

| AVDD    | AVDD    | _   | PWR | _   | 模拟正电源                     |

| AVSS    | AVSS    | _   | PWR | _   | 模拟负电源                     |

注: I/T: 输入类型;

OPT: 通过寄存器选项来配置;

CMOS: CMOS 输出; ST: 施密特触发输入;

LXT: 外部低频晶体振荡器;

O/T: 输出类型;

PWR: 电源;

NMOS: NMOS 输出;

AN: 模拟信号;

HXT:外部高频晶体振荡器。

## 极限参数

| V <sub>SS</sub> -0.3V~6.0V               | 电源供应电压  |

|------------------------------------------|---------|

| $V_{SS}$ -0.3 $V$ $\sim V_{DD}$ +0.3 $V$ | 端口输入电压  |

| 50°C~125°C                               | 储存温度    |

| 40°C~85°C                                | 工作温度    |

| 80mA                                     |         |

| 80mA                                     | IoL 总电流 |

| 500mW                                    | 总功耗     |

注:这里只强调额定功率,超过极限参数所规定的范围将对芯片造成损害,无 法预期芯片在上述标示范围外的工作状态,而且若长期在标示范围外的条 件下工作,可能影响芯片的可靠性。

## 直流电气特性

以下表格中参数测量结果可能受多个因素影响,如振荡器类型、工作电压、工作频率、引脚负载状况、温度和程序指令等等。

## 工作电压特性

Ta=-40°C~85°C

| 符号       | 参数          | 测试条件                        | 最小  | 典型 | 最大  | 单位 |

|----------|-------------|-----------------------------|-----|----|-----|----|

|          | 工作电压 – HIRC | f <sub>SYS</sub> =4MHz      | 2.2 | _  | 5.5 |    |

|          |             | f <sub>SYS</sub> =8MHz      | 2.2 | _  | 5.5 | V  |

|          |             | f <sub>SYS</sub> =12MHz     | 2.7 | _  | 5.5 |    |

|          |             | f <sub>SYS</sub> =4MHz      | 2.2 | _  | 5.5 |    |

| $V_{DD}$ | <br> 工作电压   | f <sub>SYS</sub> =8MHz      | 2.2 | _  | 5.5 | V  |

|          | 工作电压一口工     | f <sub>SYS</sub> =12MHz     | 2.7 | _  | 5.5 | V  |

|          |             | f <sub>SYS</sub> =16MHz     | 3.3 | _  | 5.5 |    |

| -        | 工作电压 – LXT  | f <sub>SYS</sub> =32.768kHz | 2.2 | _  | 5.5 | V  |

|          | 工作电压 – LIRC | f <sub>SYS</sub> =32kHz     | 2.2 |    | 5.5 | V  |

## 工作电流特性

Ta=-40°C~85°C

| 符号       | 工作模式                                                                         |                        | 测试条件                        | 最小  | 典型  | 最大  | 单位 |

|----------|------------------------------------------------------------------------------|------------------------|-----------------------------|-----|-----|-----|----|

| 17.5     | 上下铁八                                                                         | V <sub>DD</sub>        | 条件                          | 取小  | 典型  | 取入  | 半江 |

|          | 低速模式 – LIRC                                                                  | 2.2V                   |                             | _   | 15  | 30  |    |

|          |                                                                              | 3V                     | $f_{SYS}=32kHz$             | _   | 18  | 36  | μΑ |

|          |                                                                              | 5V                     |                             | _   | 30  | 50  |    |

|          |                                                                              | 2.2V                   |                             | _   | 15  | 30  |    |

|          | 低速模式 – LXT                                                                   | 3V                     | f <sub>sys</sub> =32.768kHz | _   | 18  | 36  | μΑ |

|          |                                                                              | 5V                     |                             | _   | 30  | 50  |    |

|          | $ \begin{array}{c c} 2.2V \\ \hline 3V \\ \hline 5V \end{array} $ $f_{SYS}=$ | 2.2V                   |                             | _   | 0.3 | 0.5 |    |

| $I_{DD}$ |                                                                              | f <sub>SYS</sub> =4MHz | _                           | 0.4 | 0.6 | mA  |    |

|          |                                                                              | 5V                     |                             | _   | 0.8 | 1.2 |    |

|          |                                                                              | 2.2V                   |                             | _   | 0.6 | 1.0 |    |

|          | 快速模式 – HIRC                                                                  | 3V                     | $f_{SYS}=8MHz$              | _   | 0.8 | 1.2 | mA |

|          |                                                                              | 5V                     |                             | _   | 1.6 | 2.4 |    |

|          |                                                                              | 2.7V                   |                             | _   | 1.0 | 1.4 |    |

|          |                                                                              | 3V                     | $f_{SYS}=12MHz$             | _   | 1.2 | 1.8 | mA |

|          |                                                                              | 5V                     |                             | _   | 2.4 | 3.6 |    |

Rev.1.21 18 2021-11-01

| <i>ケ</i> ケ ロ      | 工作措士       |                        | 测试条件                    | 旦小  | <b>—</b> #II | 旦十   | 出心 |

|-------------------|------------|------------------------|-------------------------|-----|--------------|------|----|

| 符号                | 工作模式       | $V_{DD}$               | 条件                      | 最小  | 典型           | 最大   | 单位 |

|                   |            | 2.2V                   |                         | _   | 200          | 500  |    |

|                   | 3V         | f <sub>SYS</sub> =4MHz | _                       | 250 | 800          | μΑ   |    |

|                   | 5V         |                        | _                       | 500 | 1300         |      |    |

|                   |            | 2.2V                   |                         | _   | 320          | 700  |    |

|                   |            | 3V                     | f <sub>SYS</sub> =8MHz  | _   | 500          | 1000 | μΑ |

| $I_{\mathrm{DD}}$ | 快速模式 – HXT | 5V                     |                         | _   | 1000         | 1600 |    |

|                   |            | 2.7V                   |                         | _   | 0.7          | 1.2  |    |

|                   |            | 3V                     | $f_{SYS}=12MHz$         | _   | 0.75         | 1.60 | mA |

|                   |            | 5V                     |                         | _   | 2.2          | 3.0  |    |

|                   |            | 3.3V                   | f <sub>sys</sub> =16MHz | _   | 1.5          | 3.0  | mA |

|                   |            | 5V                     | ISYS-101VIIIZ           |     | 2.5          | 5.0  | ША |

- 注: 当使用该表格电气特性数据时,以下几点需注意:

- 1. 任何数字输入都设置为非浮空的状态。

- 2. 所有测量都在无负载且所有外围功能关闭的条件下进行。

- 3. 无直流电流路径。

- 4. 所有工作电流数值是在执行连续的 NOP 指令循环程序下测得。

#### 待机电流特性

Ta=25℃,除非另有说明

| <i>5</i> /5 🗆 | <b>√+</b> +⊓ + <del></del> + <del>+</del> + |                 | 测试条件                                        | <b>□</b> .l. | # #1 | 日上   | 最大    | * 1* |

|---------------|---------------------------------------------|-----------------|---------------------------------------------|--------------|------|------|-------|------|

| 符号            | 待机模式                                        | V <sub>DD</sub> | 条件                                          | 最小           | 典型   | 最大   | @85°C | 单位   |

|               |                                             | 2.2V            |                                             |              | 0.8  | 1.2  | 10.0  |      |

|               |                                             | 3V              | WDT off                                     | _            | 0.8  | 1.2  | 10.0  | μΑ   |

|               | 休眠模式                                        | 5V              |                                             | _            | 1.0  | 1.5  | 12.0  |      |

|               | 7个叫(天工)                                     | 2.2V            |                                             | _            | 1.2  | 2.4  | 10.0  |      |

|               |                                             | 3V              | WDT on                                      | _            | 1.5  | 3.0  | 12.0  | μΑ   |

|               |                                             | 5V              |                                             | _            | 3    | 5    | 15    |      |

|               | 空闲模式 0 – LIRC 3V<br>5V<br>2.2V              | 2.2V            |                                             | _            | 2.4  | 4.0  | 12.0  |      |

| :             |                                             | 3V              | $f_{SUB}$ on                                | _            | 3    | 5    | 15    | μΑ   |

|               |                                             | 5V              |                                             | _            | 5    | 10   | 18    |      |

|               |                                             | 2.2V            |                                             | _            | 2.4  | 4.0  | 12.0  |      |

| $I_{STB}$     |                                             | 3V              | $f_{SUB}$ on                                | _            | 3    | 5    | 15    | μΑ   |

|               |                                             | 5V              |                                             | _            | 5    | 10   | 18    |      |

|               |                                             | 2.2V            |                                             | _            | 144  | 200  | 240   |      |

|               |                                             | 3V              | f <sub>SUB</sub> on, f <sub>SYS</sub> =4MHz | _            | 180  | 250  | 300   | μΑ   |

|               |                                             | 5V              |                                             | _            | 400  | 600  | 720   |      |

|               |                                             | 2.2V            |                                             | _            | 288  | 400  | 480   |      |

|               | 空闲模式 1 – HIRC                               | 3V              | $f_{SUB}$ on, $f_{SYS}=8MHz$                | _            | 360  | 500  | 600   | μΑ   |

|               |                                             | 5V              |                                             | _            | 600  | 800  | 960   |      |

|               |                                             | 2.7V            |                                             |              | 432  | 600  | 720   |      |

|               |                                             | 3V              | <del>-</del>                                | _            | 540  | 750  | 900   | μΑ   |

|               |                                             | 5V              |                                             | _            | 800  | 1200 | 1440  |      |

| 符号               | <b>往扣措→</b>  |          | 测试条件                   | 旦小       | <b>д</b> #II | 旦上   | 最大    | 单位    |

|------------------|--------------|----------|------------------------|----------|--------------|------|-------|-------|

| 175              | 待机模式<br>     | $V_{DD}$ | 条件                     | 最小       | 典型           | 最大   | @85°C | 半江    |

|                  |              | 2.2V     | f <sub>SYS</sub> =4MHz | _        | 144          | 200  | 240   |       |

|                  |              | 3V       |                        | _        | 180          | 250  | 300   | μΑ    |

|                  |              | 5V       |                        | _        | 600          | 800  | 960   |       |

|                  |              | 2.2V     |                        | _        | 288          | 400  | 480   |       |

|                  |              | 3V       | f <sub>SYS</sub> =8MHz | Hz — 360 | 360          | 500  | 600   | μΑ    |

| I <sub>STB</sub> | 空闲模式 1 – HXT | 5V       |                        | _        | 800          | 1200 | 1440  |       |

|                  |              | 2.7V     |                        | _        | 432          | 600  | 720   | μΑ    |

|                  |              | 3V       | $f_{SYS}=12MHz$        | _        | 540          | 750  | 900   |       |

|                  |              | 5V       |                        | _        | 1200         | 2000 | 2400  |       |

|                  |              | 3.3V     | f -16MHz               |          | 1.1          | 1.6  | 1.9   | 122 A |

|                  |              | 5V       | $f_{SYS}=16MHz$        | _        | 1.6          | 2.4  | 3.0   | mA    |

- 注: 当使用该表格电气特性数据时,以下几点需注意:

- 1. 任何数字输入都设置为非浮空的状态。

- 2. 所有测量都在无负载且所有外围功能关闭的条件下进行。

- 3. 无直流电流路径。

- 4. 所有待机电流数值都是在 HALT 指令执行后即停止执行所有指令后测得。

## 交流电气特性

以下表格中参数测量结果可能受多个因素影响,如振荡器类型、工作电压、工 作频率和温度等等。

#### 内部高速 RC 振荡器 HIRC 频率精准度

程序烧录时,烧录器会调整 HIRC 振荡器使其工作在用户选择的 HIRC 频率和工作电压  $(3V ext{ of } 5V)$  条件下。

| 符号            | 参数                        | 沙                          | 训试条件       | 最小    | 典型 | 最大    | 单位    |

|---------------|---------------------------|----------------------------|------------|-------|----|-------|-------|

| 1ग फ          | <b>少</b> 奴                | $\mathbf{V}_{\mathtt{DD}}$ | 温度         | 取小    | 典型 | 取入    | 半江    |

|               | 通过烧录器调整后的 4MHz<br>HIRC 频率 | 3V/5V                      | 25°C       | -1%   | 4  | +1%   |       |

|               |                           | 3 V / 3 V                  | -40°C~85°C | -2%   | 4  | +2%   | MHz   |

|               |                           | 2.2V~5.5V                  | 25°C       | -2.5% | 4  | +2.5% | WITIZ |

|               |                           | 2.2 V~3.3 V                | -40°C~85°C | -3%   | 4  | +3%   |       |

|               | 通过烧录器调整后的 8MHz            | 3V/5V                      | 25°C       | -1%   | 8  | +1%   |       |

| $ m f_{HIRC}$ |                           | 3 4 7 3 4                  | -40°C~85°C | -2%   | 8  | +2%   | MHz   |

| IHIRC         | HIRC 频率                   | 2.2V~5.5V                  | 25°C       | -2.5% | 8  | +2.5% | MITIZ |

|               |                           |                            | -40°C~85°C | -3%   | 8  | +3%   |       |

|               |                           | 5V                         | 25°C       | -1%   | 12 | +1%   | MII   |

| II I          | 通过烧录器调整后的 12MHz           | J V                        | -40°C~85°C | -2%   | 12 | +2%   |       |

|               | HIRC 频率                   | 2.7V~5.5V                  | 25°C       | -2.5% | 12 | +2.5% | MHz   |

|               |                           | 2.7 V~3.3 V                | -40°C~85°C | -3%   | 12 | +3%   |       |

- 注: 1. 烧录器可在 3V/5V 这两个可选的固定电压下对 HIRC 频率进行调整,在此提供  $V_{DD}=3V/5V$  时的参数值。

- 2. 3V/5V 表格列下面提供的是全压条件下的参数值。对于电压范围在 2.2V~3.6V 的应用,建议烧录器电压固定在 3V;对于电压范围在 3.3V~5.5V 的应用,建议烧录器电压固定在 5V。

Rev.1.21 20 2021-11-01

3. 表格中提供的最小和最大误差值仅在对应的烧录器调整频率下有效。当烧录器已将 HIRC 调整为某一固定频率,此后再通过程序使用振荡器控制位将其频率改为其它值时,频率误差范围将增加到±20%。

## 内部低速振荡器 LIRC 电气特性

| 符号          | 参数        |                            | 最小         | 典型   | 最大 | 单位   |     |

|-------------|-----------|----------------------------|------------|------|----|------|-----|

| 175         |           | $\mathbf{V}_{\mathtt{DD}}$ | 温度         | 取小   | 典型 | 取入   | 半加  |

| flirc       | LIRC 频率   | 2.2V~5.5V                  | -40°C~85°C | -10% | 32 | +10% | kHz |

| $t_{START}$ | LIRC 启动时间 | _                          | -40°C~85°C |      | _  | 100  | μs  |

## 外部低速晶体振荡器 LXT 电气特性

Ta=25°C

| 符号                 | 参数       | ž                          | 则试条件 | 最小    | 典型         | 最大   | 单位 |

|--------------------|----------|----------------------------|------|-------|------------|------|----|

| 1য় ড              |          | $\mathbf{V}_{\mathtt{DD}}$ | 条件   | 取小    | <b>兴</b> 至 | 取入   | 中心 |

| $f_{LXT}$          | LXT 频率   | 2.2V~5.5V                  | _    | _     | 32768      |      | Hz |

| Duty Cycle         | 占空比      | _                          | _    | 40    | _          | 60   | %  |

|                    | LXT 启动时间 | 3V                         | _    | _     | _          | 1000 |    |

| t <sub>START</sub> | LXI 后初时间 | 5V                         | _    |       | _          | 1000 | ms |

| R <sub>NEG</sub>   | 负阻       | 2.2V                       | _    | 3×ESR | _          | _    | Ω  |

注: C1, C2 和  $R_P$  为外部元件。C1=C2=10pF, $R_P$ =10M $\Omega$ 。CL=7pF,ESR=30k $\Omega$ 。

## 工作频率电气特性曲线图

#### 系统上电时间电气特性

Ta=-40°C~85°C

| 符号                | 参数                                       |                           | 测试条件                                                       | 最小 | 曲刑   | 最大  | 并位             |

|-------------------|------------------------------------------|---------------------------|------------------------------------------------------------|----|------|-----|----------------|

| 17 5              |                                          | $\mathbf{V}_{	extsf{DD}}$ | 条件                                                         | 取小 | 典型   | 取入  | 半亚             |

|                   |                                          |                           | $f_{SYS} = f_H \sim f_H/64,  f_H = f_{HXT}$                | _  | 128  | _   | $t_{\rm HXT}$  |

|                   | 系统启动时间<br>(从 fsys off 的状态下唤醒)            | _                         | $f_{SYS}=f_H\sim f_H/64$ , $f_H=f_{HIRC}$                  | _  | 16   | _   | $t_{\rm HIRC}$ |

|                   |                                          |                           | $f_{SYS} = f_{SUB} = f_{LXT}$                              | _  | 1024 | _   | $t_{LXT}$      |

|                   |                                          |                           | $f_{SYS} = f_{SUB} = f_{LIRC}$                             | _  | 2    | _   | $t_{\rm LIRC}$ |

| t <sub>SST</sub>  | 系统启动时间<br>(从 f <sub>sys</sub> on 的状态下唤醒) | _                         | $f_{SYS} = f_H \sim f_H/64$ , $f_H = f_{HXT}$ 或 $f_{HIRC}$ |    | 2    | _   | t <sub>H</sub> |

|                   | ( M Isys OII 时状态下映框 )                    |                           | $f_{SYS}$ = $f_{SUB}$ = $f_{LXT}$ 或 $f_{LIRC}$             | _  | 2    | _   | $t_{ m SUB}$   |

|                   | 系统速度切换时间                                 |                           | $f_{\text{HXT}}  \text{off} \rightarrow \text{on}$         | _  | 1024 |     | $t_{\rm HXT}$  |

|                   | (快速模式→低速模式或                              | _                         | $f_{HIRC}$ off $\rightarrow$ on                            | _  | 16   | _   | $t_{\rm HIRC}$ |

|                   | 低速模式 → 快速模式)                             |                           | $f_{LXT}$ off $\rightarrow$ on                             | _  | 1024 | _   | $t_{LXT}$      |

|                   | 系统复位延迟时间<br>(上电复位或 LVR 硬件复位)             | _                         | RR <sub>POR</sub> =5V/ms                                   | 14 | 16   | 18  |                |

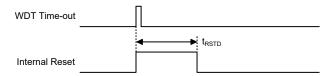

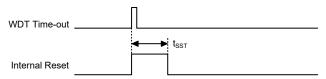

| t <sub>RSTD</sub> | 系统复位延迟时间<br>(LVRC/WDTC/RSTC软件复位)         | _                         | _                                                          | 14 | 10   | 10  | ms             |

|                   | 系统复位延迟时间<br>(WDT溢出复位)                    |                           | _                                                          | 14 | 16   | 18  |                |

| tsreset           | 软件复位最小延迟脉宽                               |                           | _                                                          | 45 | 90   | 120 | μs             |

- 注: 1. 系统启动时间里提到的 fsys on/off 状态取决于工作模式类型以及所选的系统时钟振荡器。更多相关细节请参考系统工作模式章节。

- 2. t<sub>HIRC</sub>等符号所表示的时间单位,是对应频率值的倒数,相关频率值在前面表格有说明。例如,t<sub>HIRC</sub>=1/f<sub>HIRC</sub>, t<sub>Sys</sub>=1/f<sub>Sys</sub>等等。

- 3. 若 LIRC 被选择作为系统时钟源且在休眠模式下 LIRC 关闭,则上面表格中对应 tssr 数值还需加上 LIRC 频率表格里提供的 LIRC 启动时间 tstart。

- 4. 系统速度切换时间实际上是指新使能的振荡器的启动时间。

## 输入/输出口电气特性

## 输入/输出口(非多电源引脚)直流电气特性

Ta=-40°C~85°C

| 符号                | 参数              |                 | 测试条件                                 | 最小                   | 典型  | 最大                 | 单位 |

|-------------------|-----------------|-----------------|--------------------------------------|----------------------|-----|--------------------|----|

| 1ग फ              |                 | V <sub>DD</sub> | 条件                                   | 取小                   | 典尘  | 取入                 | 中山 |

| $V_{\rm IL}$      | I/O 口低电平输入电压    | 5V              | _                                    | 0                    | _   | 1.5                | V  |

| V IL              | (除 PD0~PD3 引脚外) |                 |                                      | 0                    | _   | $0.2V_{\text{DD}}$ | ·  |

| $V_{\mathrm{IH}}$ | I/O 口高电平输入电压    | 5V              | _                                    | 3.5                  | _   | 5.0                | V  |

| VIH               | (除 PD0~PD3 引脚外) | _               | _                                    | $0.8V_{\mathrm{DD}}$ | _   | $V_{DD}$           | v  |

| T                 | I/O 口灌电流        | 3V              | $V_{OL}=0.1V_{DD}$                   | 16                   | 32  | _                  | A  |

| $I_{OL}$          | (除 PD0~PD3 引脚外) | 5V              | V <sub>OL</sub> -U.1 V <sub>DD</sub> | 32                   | 65  | _                  | mA |

| т                 | I/O 口源电流        | 3V              | V -0.0V                              | -4                   | -8  | _                  | 4  |

|                   | (除 PD0~PD3 引脚外) | 5V              | $V_{OH}=0.9V_{DD}$                   | -8                   | -16 | _                  | mA |

Rev.1.21 22 2021-11-01

| 符号               | 参数                  |          | 测试条件                                                                | 最小  | 典型 | 最大  | 单位  |

|------------------|---------------------|----------|---------------------------------------------------------------------|-----|----|-----|-----|

| 何亏               |                     | $V_{DD}$ | 条件                                                                  | 取小  | 典型 | 取入  | 半四  |

| D                | I/O 口上拉电阻 (注)       | 3V       |                                                                     | 20  | 60 | 100 | kΩ  |

| $R_{PH}$         | (除 PD0~PD3 引脚外)     | 5V       | _                                                                   | 10  | 30 | 50  | K22 |

| т                | I/O 口输入漏电流          | 3V       | V <sub>IN</sub> =V <sub>DD</sub> 或 V <sub>IN</sub> =V <sub>SS</sub> |     |    | + 1 |     |

| ILEAK            | (除 PD0~PD3 引脚外)     | 5V       | V <sub>IN</sub> =V <sub>DD</sub> 以 V <sub>IN</sub> =V <sub>SS</sub> |     |    | ±1  | μΑ  |

| $t_{TCK}$        | TM 时钟输入引脚最小输入<br>脉宽 | _        | _                                                                   | 0.3 |    | _   | μs  |

| t <sub>INT</sub> | 外部中断引脚最小输入脉宽        | _        | _                                                                   | 10  | _  | _   | μs  |

注: R<sub>PH</sub> 内部上拉电阻值的计算方法是: 将引脚接地并设置为输入且使能上拉电阻功能, 然后在特定电源电压下测量该引脚上的电流, 最后电压除以测量的电流值从而得到此上拉电阻值。

## 输入/输出口(多电源引脚)直流电气特性

Ta=-40°C~85°C

| 符号              | 参数                               |                           | 测试条件                                                                                       | 最小                                                      | 典型   | 最大                                           | 单位   |

|-----------------|----------------------------------|---------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------|------|----------------------------------------------|------|

| 175             | 多奴                               | $\mathbf{V}_{	extsf{DD}}$ | 条件                                                                                         | 取 小                                                     | 典型   | 取 <b>八</b>                                   | 半世   |

| $V_{DD}$        | PD0~PD3 引脚电源<br>V <sub>DD</sub>  | _                         | _                                                                                          | 2.2                                                     | 5.0  | 5.5                                          | V    |

| $V_{\rm DDIO}$  | PD0~PD 引脚电源<br>V <sub>DDIO</sub> | _                         | _                                                                                          | 2.2                                                     | _    | $V_{DD}$                                     | V    |

| V               | PD0~PD3 引脚低电                     | 5V                        | 引脚电源=V <sub>DD</sub> 或 V <sub>DDIO</sub><br>V <sub>DDIO</sub> =V <sub>DD</sub>             | 0                                                       | _    | 1.5                                          | V    |

| $V_{IL}$        | 平输入电压                            | _                         | 引脚电源 = V <sub>DD</sub> 或 V <sub>DDIO</sub>                                                 | 0                                                       | _    | 0.2<br>(V <sub>DD</sub> /V <sub>DDIO</sub> ) | v    |

| N/              | PD0~PD3 引脚高电                     | 5V                        | 引脚电源=V <sub>DD</sub> 或 V <sub>DDIO</sub><br>V <sub>DDIO</sub> =V <sub>DD</sub>             | 3.5                                                     | _    | 5.0                                          | V    |

| V <sub>IH</sub> | 平输入电压                            | _                         | 引脚电源 = V <sub>DD</sub> 或 V <sub>DDIO</sub>                                                 | $\begin{array}{c} 0.8 \\ (V_{DD}/V_{DDIO}) \end{array}$ | _    | $V_{DD}/V_{DDIO}$                            | v    |

|                 |                                  | 3V                        | V <sub>OL</sub> =0.1(V <sub>DD</sub> 或 V <sub>DDIO</sub> )                                 | 16                                                      | 32   | _                                            | mA   |

| $I_{OL}$        | PD0~PD3 引脚灌电                     | 5V                        | V <sub>DDIO</sub> =V <sub>DD</sub>                                                         | 32                                                      | 65   | _                                            | mA   |

| TOL             | 流                                | 5V                        | $V_{OL}$ =0.1( $V_{DD}$ 或 $V_{DDIO}$ ) $V_{DDIO}$ =3 $V$                                   | 20                                                      | 40   | _                                            | mA   |

|                 |                                  | 3V                        | V <sub>OH</sub> =0.9(V <sub>DD</sub> 或 V <sub>DDIO</sub> )                                 | -4                                                      | -8   | _                                            |      |

| $I_{OH}$        | PD0~PD3 引脚源电                     | 5V                        | $V_{\rm DDIO} = V_{\rm DD}$                                                                | -8                                                      | -16  | _                                            | mA   |

| IOH             | 流                                | 5V                        | V <sub>OH</sub> =0.9(V <sub>DD</sub> 或 V <sub>DDIO</sub> )<br>V <sub>DDIO</sub> =3V        | -2.5                                                    | -5.0 | _                                            | IIIA |

|                 |                                  | 3V                        | 引脚电源 = V <sub>DD</sub> 或 V <sub>DDIO</sub>                                                 | 20                                                      | 60   | 100                                          | kΩ   |

| $R_{PH}$        | PD0~PD3 引脚上拉                     | 5V                        | $V_{DDIO}=V_{DD}$                                                                          | 10                                                      | 30   | 50                                           | kΩ   |

| INPH            | 电阻(注)                            | 5V                        | 引脚电源=V <sub>DD</sub> 或 V <sub>DDIO</sub><br>V <sub>DDIO</sub> =3V                          | 36                                                      | 110  | 180                                          | kΩ   |

| ILEAK           | PD0~PD3 引脚输入<br>漏电流              | 5V                        | V <sub>IN</sub> =V <sub>SS</sub> 或<br>V <sub>IN</sub> =V <sub>DD</sub> 或 V <sub>DDIO</sub> | _                                                       | _    | ±1                                           | μА   |

注: RpH 内部上拉电阻值的计算方法是: 将引脚接地并设置为输入且使能上拉电阻功能, 然后在特定电源电压下测量该引脚上的电流, 最后电压除以测量的电流值从而得到此上拉电阻值。

## 存储器电气特性

Ta=-40℃~85℃,除非另有说明

| 符号                | 参数                    |          | 测试条件      | 最小                 | 典型  | 最大                 | 单位   |

|-------------------|-----------------------|----------|-----------|--------------------|-----|--------------------|------|

| 17 5              | <b>多</b> 奴            | $V_{DD}$ | 条件        | 取小                 | 典型  | 取入                 | 半世   |

| $V_{RW}$          | 读/写工作电压               | _        | _         | $V_{\text{DDmin}}$ | _   | $V_{\text{DDmax}}$ | V    |

| Flash             | 程序存储器                 |          |           |                    |     |                    |      |

| $t_{\rm FER}$     | IAP 擦除时间              | _        | FWERTS=0  | _                  | 3.2 | 3.9                | ms   |

| LFER              | IAI 1家隊印刊             | _        | FWERTS=1  | _                  | 3.7 | 4.5                | 1115 |

| $t_{ m FWR}$      | IAP 写时间               | _        | FWERTS=0  | _                  | 2.2 | 2.7                | , mg |

| LFWR              | IAF 与时间               | _        | FWERTS=1  | _                  | 3.0 | 3.6                | ms   |

| ЕР                | 存储单元耐久性 – Flash 程序存储器 |          | _         | 10K                |     | _                  | E/W  |

| $t_{RETD}$        | ROM 数据保存时间            | _        | Ta=25°C   | _                  | 40  |                    | Year |

| $t_{ACTV}$        | ROM 激活时间 – 从暂停模式唤醒    | _        | _         | 32                 | _   | 64                 | μs   |

| 数据Ⅰ               | EEPROM 存储器            |          |           | ,                  |     |                    |      |

| 4                 | 擦除时间                  | _        | EWERTS=0  | _                  | 3.2 | 3.9                | mg   |

| t <sub>EEER</sub> | 1余  休日                | _        | EWERTS=1  | _                  | 3.7 | 4.5                | ms   |

|                   | 写时间(字节模式)             | _        | EWERTS=0  | _                  | 5.4 | 6.6                |      |

| ļ_                | 与时间(子口侯八)             | _        | EWERTS=1  | _                  | 6.7 | 8.1                | , mg |

| $t_{\rm EEWR}$    | 写时间(页模式)              | _        | EWERTS=0  | _                  | 2.2 | 2.7                | ms   |

|                   | 与时间(贝侯八)              | _        | EWERTS=1  | _                  | 3.0 | 3.6                |      |

| E <sub>P</sub>    | 存储单元耐久性 – EEPROM 存储器  |          | _         | 100K               |     | _                  | E/W  |

| $t_{RETD}$        | 数据保存时间                | _        | Ta=25°C   | _                  | 40  | _                  | Year |

| RAM               | 数据存储器                 |          |           |                    |     |                    |      |

| $V_{DR}$          | RAM 数据保存电压            | _        | 单片机处于休眠模式 | 1.0                | _   | _                  | V    |

注: 1. 在计算从暂停模式唤醒的系统总启动时间时,还需加上 ROM 激活时间 t<sub>ACTV</sub>。

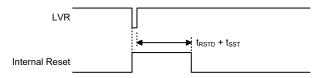

## LVR 电气特性

Ta=-40°C~85°C

| 符号               | 参数                         |                   | 测试条件                          | 最小   | 曲刑   | <b>旱</b> 十 | 单位           |

|------------------|----------------------------|-------------------|-------------------------------|------|------|------------|--------------|

| 打写               | 1寸万   参数                   |                   | 条件                            | 取小   | 典型   | 取入         | 中江           |

|                  |                            | LVR 使能, 电压选择 2.1V |                               | 2.1  |      |            |              |

| V <sub>LVR</sub> | V <sub>LVR</sub>   低电压复位电压 |                   | LVR 使能,电压选择 2.55V             | -3%  | 2.55 | +3%        | $ _{\rm V} $ |

| V LVR            | 似电压复型电压 <br>               |                   | LVR 使能, 电压选择 3.15V            | -370 | 3.15 | +370       | V            |

|                  |                            |                   | LVR 使能, 电压选择 3.8V             |      | 3.8  |            |              |

| т                | <br> LVR 工作电流              | 3V                | LVR 使能,V <sub>LVR</sub> =2.1V | _    | _    | 10         |              |

| ILVROP           | ILVROP LVR 工作电流            | 5V                | LVK (文邦, V LVR—2.1 V          | _    | 10   | 15         | μΑ           |

| $I_{LVR}$        | LVR 使能的额外电流                | 5V                | _                             |      |      | 14         | μА           |

| $t_{LVR}$        | 产生 LVR 复位的低电压最<br>短保持时间    |                   | _                             | 120  | 240  | 480        | μs           |

Rev.1.21 24 2021-11-01

<sup>2. &</sup>quot;E/W"表示擦/写次数。

## 模拟前端电路特性

## 运算放大器电气特性

Ta=-40°C~85°C,除非另有说明

| <i>አ</i> ሉ 🗆 | <del>会</del> 米L |                 | 测试条件                                                                                                                                                            | <b>□</b> ,l,         | #### | 日上                   | 出心    |

|--------------|-----------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------|----------------------|-------|

| 符号           | 参数              | V <sub>DD</sub> | 条件                                                                                                                                                              | 最小                   | 典型   | 最大                   | 単位    |

| $I_{OPA}$    | OPA 工作电流        | 3V              | $V_P = V_N = 1/2V_{DD}$                                                                                                                                         | _                    | _    | 650                  | μA    |

| Aol          | OPA 开环增益        | 3V              | _                                                                                                                                                               | 80                   | 100  | _                    | dB    |

| Ro           | 输出阻值            | 2.4V~<br>3.6V   | Ta=0°C~50°C,<br>R <sub>LOAD</sub> =50kΩ<br>0.2V <v<sub>OP<v<sub>DD - 1.4V<br/>( 电压跟随器配置 )</v<sub></v<sub>                                                       | _                    | _    | 260                  | Ω     |

| $I_{OS}$     | 输入失调电流          | 2.4V~<br>3.6V   | Ta=0°C~50°C                                                                                                                                                     | _                    | ±5   | _                    | nA    |

| TC           | 失调电压温度系数        | 3V              | Ta=0°C~50°C                                                                                                                                                     | _                    | _    | ±20                  | μV/°C |

| GBW          | 增益带宽            | 3V              | $ \begin{array}{l} \text{Ta=25°C, R}_{\text{L}} = 1 \text{M}\Omega, \\ \text{C}_{\text{L}} = 60 \text{pF, V}_{\text{IN}} = \text{V}_{\text{CM}}/2 \end{array} $ | 100                  |      | _                    | kHz   |

| Vos          | 输入失调电压          | 3V              | 未校准                                                                                                                                                             | -15                  | _    | 15                   | mV    |

| $V_{CM}$     | OPA 共模电压范围      | 3V              | _                                                                                                                                                               | 0.1                  | _    | V <sub>DD</sub> -1.4 | V     |

| Vor          | OPA 最大输出电压范围    | 3V              | _                                                                                                                                                               | V <sub>SS</sub> +0.1 | _    | V <sub>DD</sub> -0.1 | V     |

## 内部参考电压特性

Ta=-40°C~85°C,除非另有说明

| 符号参数               |               | 测试条件            |                              | 最小  | 典型   | 最大   | 单位     |

|--------------------|---------------|-----------------|------------------------------|-----|------|------|--------|

|                    |               | V <sub>DD</sub> | 条件                           | 取小  | - 典型 | 取入   | 半江     |

| $V_{IREF}$         | 内部参考电压        | 3V              | IREFEN=1,<br>PVREF=10000000B | -3% | 2.0  | +3%  | V      |